在两个分开的Always语句中,类似的语句怎么输出结果步一样?

时间:10-02

整理:3721RD

点击:

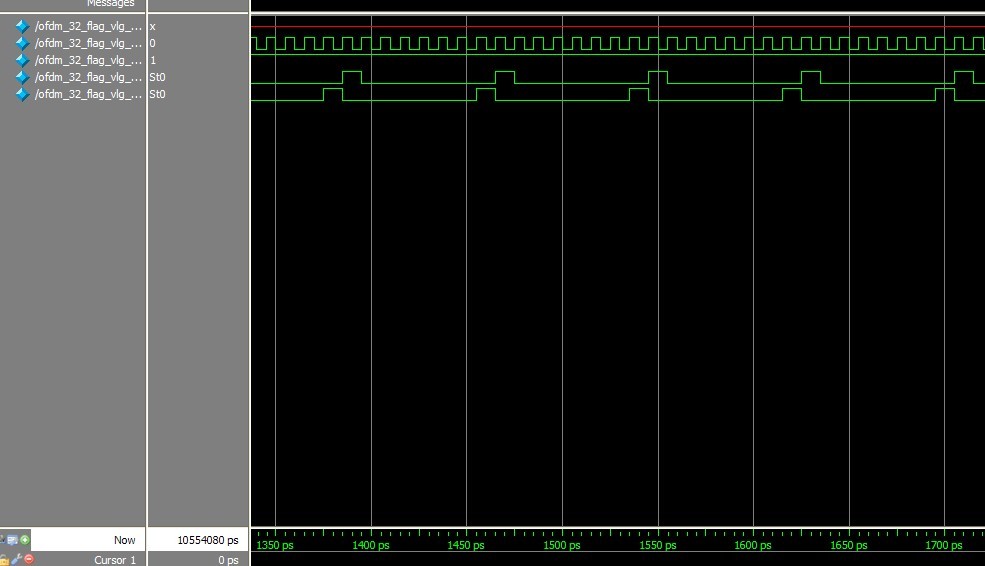

在两个分开的Always语句中,相同的语句怎么输出结果步一样?譬如我想在一个8点为一帧的数据中,让一个信号在第一点为高电平,另外一个信号在最后一个点的输出数据为高,其余都为低。其实8点的FFT变换的输入sink_sop和sink_eop就是这种信号!我采用了两种不同方法来写,怎么输出结果步一样?还有我采用该方法写sink-sop,sink_eop的方法对吗。方法一,在不同的ALWAS语句中实现用2计数器计数,图一所示。

module ofdm_32_flag(reset,clk,flag,a);

input clk,reset;

output reg flag;

output reg a;

reg [2:0] cnt,cnt_a;

always @(posedge clk)

begin

if(!reset) begin

cnt <= 0;[attach]485373[/attach][attach]485373[/attach]

flag <= 0;

end

else

begin cnt <= cnt + 1;

if(cnt == 0)

flag<= 1;

else begin flag<=0;end

end

end

always @(posedge clk)

begin

if(!reset) begin

cnt_a <= 0;

a <= 0;

end

else

begin cnt_a <= cnt_a + 1;

if(cnt_a== 7)

a<= 1;

else

a<=0;

end

end

方法二:用一个计数器计数,图2

always @(posedge clk)

begin

if(!reset) begin

cnt <= 0;

flag <= 0;a<=0

end

else

begin cnt <= cnt + 1;

if(cnt == 0)

a<= 1;

else if(cnt==7)flag<=1;

else begin

a<= 0;flag<=0;

end

end

end

上图没有做好,重新贴下。

在两个分开的Always语句中,相同的语句怎么输出结果步一样?譬如我想在一个8点为一帧的数据中,让一个信号在第一点为高电平,另外一个信号在最后一个点的输出数据为高,其余都为低。其实8点的FFT变换的输入sink_sop和sink_eop就是这种信号!我采用了两种不同方法来写,怎么输出结果步一样?还有我采用该方法写sink-sop,sink_eop的方法对吗。方法一,在不同的ALWAS语句中实现,用2计数器计数,图一所示。

在两个分开的Always语句中,相同的语句怎么输出结果步一样?譬如我想在一个8点为一帧的数据中,让一个信号在第一点为高电平,另外一个信号在最后一个点的输出数据为高,其余都为低。其实8点的FFT变换的输入sink_sop和sink_eop就是这种信号!我采用了两种不同方法来写,怎么输出结果步一样?还有我采用该方法写sink-sop,sink_eop的方法对吗。方法一,在不同的ALWAS语句中实现,用2计数器计数,图一所示。

个人认为该把else if(cnt==7) b<=1;改为else if(cnt==7)begin b<=1;a<= 0;end,吧?!你的第一种方法在cnt == 7时a=0,而第二种方法不是所以才有这个结果,而且难道综合的时候没有提示有latch产生吗?

没有锁存器出现啊。综合成功。锁存器在没有把所有选择情况考虑在内的话才有锁存器出现吧。你的提议怎么我看不懂。我输出的2个信号是flag和a

第二种方法中是不是a和b输出啊?

步好意思,程序帖错了。刚改过来了。步过没有关系的,就是2输出信号不一样,看得懂就行。方法就是采用2个不同的always语句。仿真几次还是这种问题啊。

cnt == 7 时,第二种方法会进入 else if 内,而不会到最后的 else 内。所以 a 不会被清为 0。

感谢,刚发现果然是你说的问题,是个语法不严谨的错误。else 后面不加begin..end该分语句会一直顺序执行。

非常感谢