跨板阻抗匹配的问题

1、两块板子的阻抗匹配改怎么做呢,比如75欧姆的阻抗匹配,是每块板子上平均匹配37.5欧姆吗?

2、接插件的阻抗需要考虑吗?

大神们帮助兄弟一下哇,现在对这块不太了解,只好来论坛求救了!

两个单板都应该是75欧姆.

两个单板信号传递的速率是多少?.

接插件没有阻抗的概念,近似为良导体.

负责任的做法是,去补习一下微波/射频中有关分布参数系统、无损传输线的原理知识。

如果你打死都不想看书,只求快速上手,可以遵循下面两个最最重要的准则:(还是建议你去补一下原理知识!)

1. 信号走线不要分岔,线宽不要突变。严禁星形走线。

2. 在信号发送端串联一个75电阻(适用于100MHz以下信号),或在信号接收端并联一个75电阻到电源或地(适用于任何信号)。

PS:实际上Guideline非常多,上面两个是最最重要的(或者说适用于新手)。接插件是有特征阻抗的,不过一般不太重要。

信号的速率是符合BT656和BT1120标准的,时钟速率不是太高。按兄弟的意思是不是一根75欧姆的阻抗匹配线,如果通过接插件分开到两个板子上的话,每块板子上的线都需要布蛇形走线,匹配到75欧姆啊?刚刚接触这一块,是在不好意思啊,麻烦兄弟了!

好的,谢谢了啊,等我把这个板子忙完,要好好看看这块。至于兄弟说的75欧姆串接和并联的形式,由于板子太小了,没有地方放那么多的电阻了。

所谓“匹配”,关键就在于输出端串联电阻或输入端并联电阻,否则就是完全没有作匹配。

至少要对时钟信号作匹配。线路等长(蛇形走线)在很多时候跟阻抗匹配相比要次要得多。

这个BT1120已经达到148.5MHZ,还不算高吗?

学习了

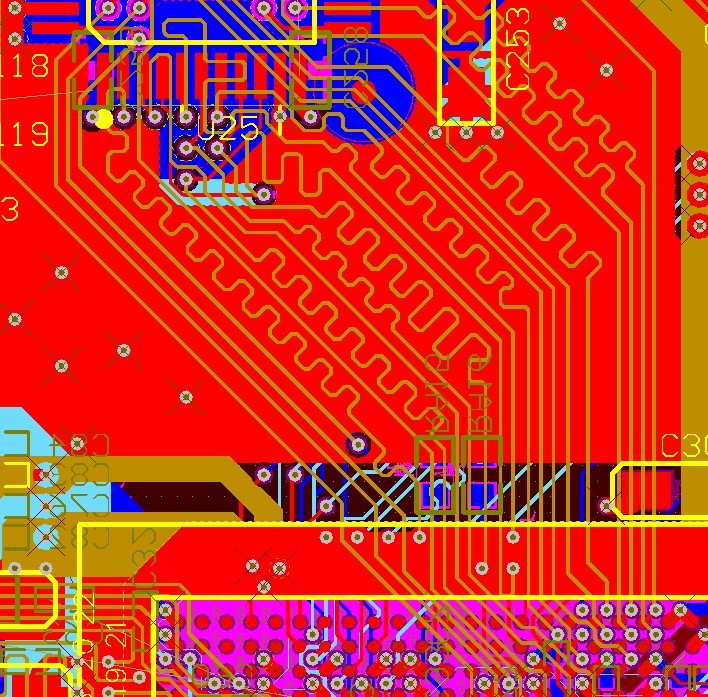

[attach]489265[/attach]回复 6# Timme

嗯,经过认真评估,打算采用兄弟所说的75欧姆阻抗并地的方式,那再问兄弟一个问题,数据接口和FPGA之间存在蛇形走线,并没有等间距,请问这些蛇形走线是不是为了等长的,想让所有的数据线到FPGA的IO口都等长啊?

真的做板端阻抗匹配, 那考慮一下 針對板對板連接線的長度.

還有線材

這也重要