DC综合分频电路的时钟约束问题

create_generated_clock -name CLKB -source [get_ports CLKA] -devide_by 4 [get_pins CLKB];

create_generated_clock -name CLKC -source [get_ports CLKA] -devide_by 8 [get_pins CLKC];

get_pins写得不对吧,在做综合之前我不知道触发器的名称啊?

另外CLKC的约束可不可以这样写:

create_generated_clock -name CLKC -source [get_pins CLKB] -devide_by 2 [get_pins CLKC];

一般我碰到这个问题是把分频后的时钟作为输出端口,最后会综合掉。

如果不作为输出端口,就等综合出电路后找出电路图中对应的pin脚。

还有哪位大牛有好点的方法没?

谢谢你的回答,

将分频时钟作为输出端口不明白,

综合出电路后找出电路图中对应的pin脚好理解

小编···假如我没一个分频器都是用计数器来写的,你的可能是用clk2生成clk4吧,我看你想那样分频。

我现在有问题啊,这个DC在分频中是否只定义分频···像这种create_generated_clock [get_pins uut4/clk256_reg/Q] -name uut4/clk256_reg/Q -source [get_ports clk] -divide_by 256

那么这个分频出来的时钟是否要约束一下呢?····这个综合后我出现了setup time的violation ,比如下面这个:

Required Actual

Endpoint Path Delay Path Delay Slack

-----------------------------------------------------------------

uut4/clk256_reg/D 196.65 34302.58 f -34105.93 (VIOLATED)

clk256_reg是在clk这个时钟控制下采样的,那么这种大概是什么原因呢?因为我这个clk256_reg的数据的确是34302.58才发生一个反向变化的,难道这种就不检验··设置falsh_path?请指导!

可以考虑 multicycle path

那么这个多周期怎么设置啊!我这个错误是有一个cell的延迟很大,具体原因我也不清楚··你看看这段话!

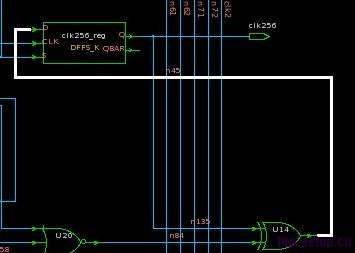

clk256是一个256的分频器!你看那个XOR2_C直接延迟34302.59那么大。附上图片

U14就是XOR2_C

Point Incr Path

-----------------------------------------------------------

clock uut4/clk256_reg/Q (fall edge) 24999.94 24999.94

uut4/clk256_reg/Q (DFFS_K) 0.00 # 24999.94 f

uut4/U14/Z (XOR2_C) 34302.59 # 59302.52 f

uut4/clk256_reg/D (DFFS_K) 0.00 59302.52 f

data arrival time 59302.52

clock clk (rise edge) 25195.25 25195.25

clock network delay (ideal) 2.00 25197.25

clock uncertainty -0.50 25196.75

uut4/clk256_reg/CLK (DFFS_K) 0.00 25196.75 r

library setup time -0.31 25196.44

data required time 25196.44

-----------------------------------------------------------

data required time 25196.44

data arrival time -59302.52

-----------------------------------------------------------

slack (VIOLATED) -34106.09

图

这个不是多周期。 看看是否需要加入buf之类增强驱动吧

对,分频时候sdc是否都要把所有的时钟(包含分频时钟)设置成ideal-network 和dont-touch属性呢?

不知道小编解决了吗?我的是holdtime的问题,但是感觉DC的分析方法有点问题