降速处理

时间:10-02

整理:3721RD

点击:

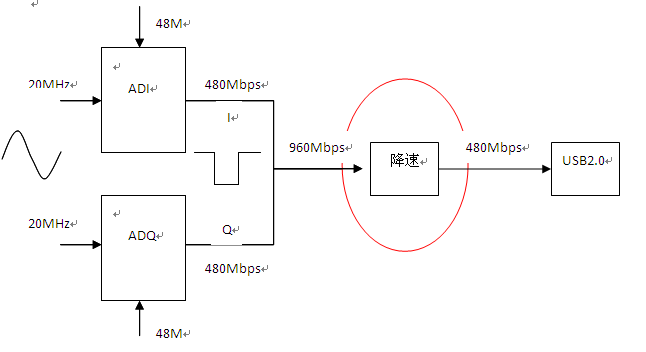

说明:图中20MHz为AD转换前的正弦信号,分为I和Q两路。 48M为采样频率,采用10位的AD。因此AD转换后的速率为480Mbps,依然为I和Q两路。将IQ两路合并后的速率就为960Mpbs。

由于USB2.0的最高速率是480Mbps,要使合并后的信号的送至USB,必须要进行降速处理。

问题所在:如何实现降速(将960Mpbs降速至480Mpbs),使得降速前后的信号信息不发生改变(即基带可以正常的解码解调而不会影响误码率的降低)。

求高手请教!不胜感激!

两个办法

1:因为是两倍,所以可以采用双寄存器缓存,即用寄存器打两拍。

如always@(posedge clk)

r1<=din;

r2<=r2;

assign data_i=r2;

2如果你发现双向传输会出现问题,那你就用异步fifo来做。

应该得将数据进行编码压缩之后再通过USB2.0输出,具体的就不太懂了

可不可以吧AD出来的数据做抽取后变为240Mbps ,在做复合呀?

两边带宽不一样,如果不压缩的话怎么降速啊?

20Mhz的信号采样频率最低得40M,那数据率最低是400mbps。不然会混叠

这样做是通过数据缓存处理的。这样做的话会有点慢!有没有什么算法是可以实现的呢?谢了