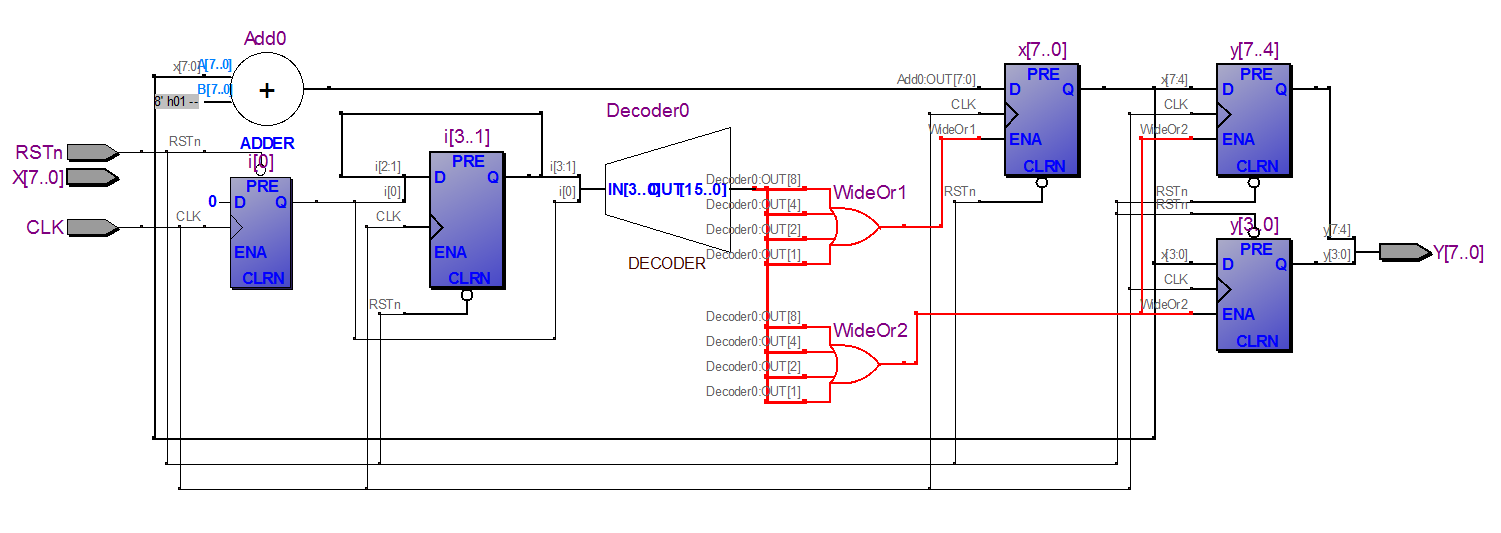

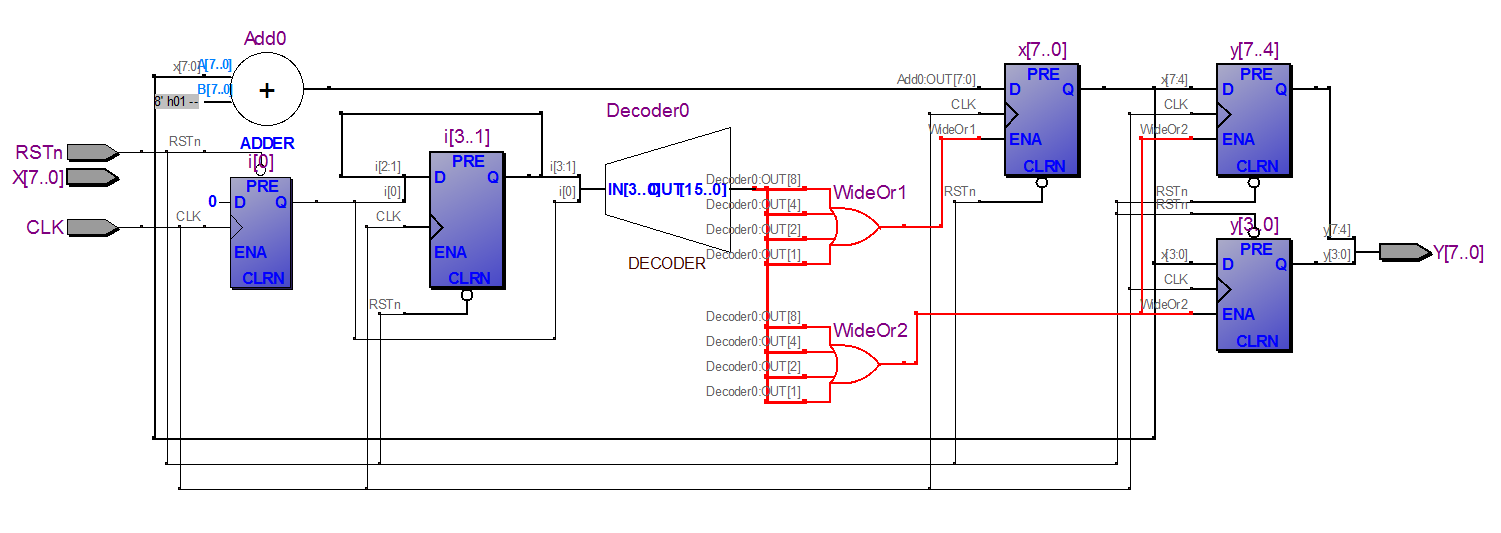

RTL原理图中,WideOr不能引出三根线吗?

时间:10-02

整理:3721RD

点击:

图中,WideOr1和WideOr2完全一样,为什么不是用一个WideOr引出三根线呢?(图下面是相关code)

- module Case_module

- (

- CLK,RSTn,

- X,

- Y

- );

- input CLK,RSTn;

- input [7:0]X;

- output [7:0]Y;reg [7:0]x;

- reg [7:0]y;reg [3:0]i;always @(posedge CLK or negedge RSTn)

- if(!RSTn)

- begin

- x <= 8'b0;

- y <= 8'h0F;

- i <= 4'b1;

- end

- else

- begin

- case(i)

- 4'b0001,4'b0010,4'b0100,4'b1000:

- begin

- x <= x + 1'b1;

- y <= x;

- i <= i << 1;

- end

- default: i <= 4'hx;

- endcase

-

- endassign Y = y;

-

- endmodule

09.output [7:0]Y;reg [7:0]x;

明显有错么,x是input,怎么可能是reg

我这代码里input X没用,要想用的话always里x<=X就行了,但这跟我的问题没有关系

哈哈,看错了大x和小x不一样!

这一步是Elaborate后的图,此时还未进行任何优化,直接由RTL翻译过来的,所以你会看到两个重复的逻辑(一个always块里有多个变量赋值的,会被拆分为多个always块,然后独立翻译为电路)。

Synthesis那一步就会进行各种化简优化了。

我试了 start analysis & synthesis等几个选项, 但是rtl viewer没有被优化,请问您说的是这个图里的某个选项吗?需要使用Synplify吗?

RTL Viewer看的就是Elaborate后的,Synthesis后的你要看Post-Mapping。

这里的Synthesis就是你图中第三项。RTL Viewer在跑完图中第二项就可以看了。

谢谢!看过您写的手动P&R的帖子,十分钦佩!