稍复杂时钟管理

时间:10-02

整理:3721RD

点击:

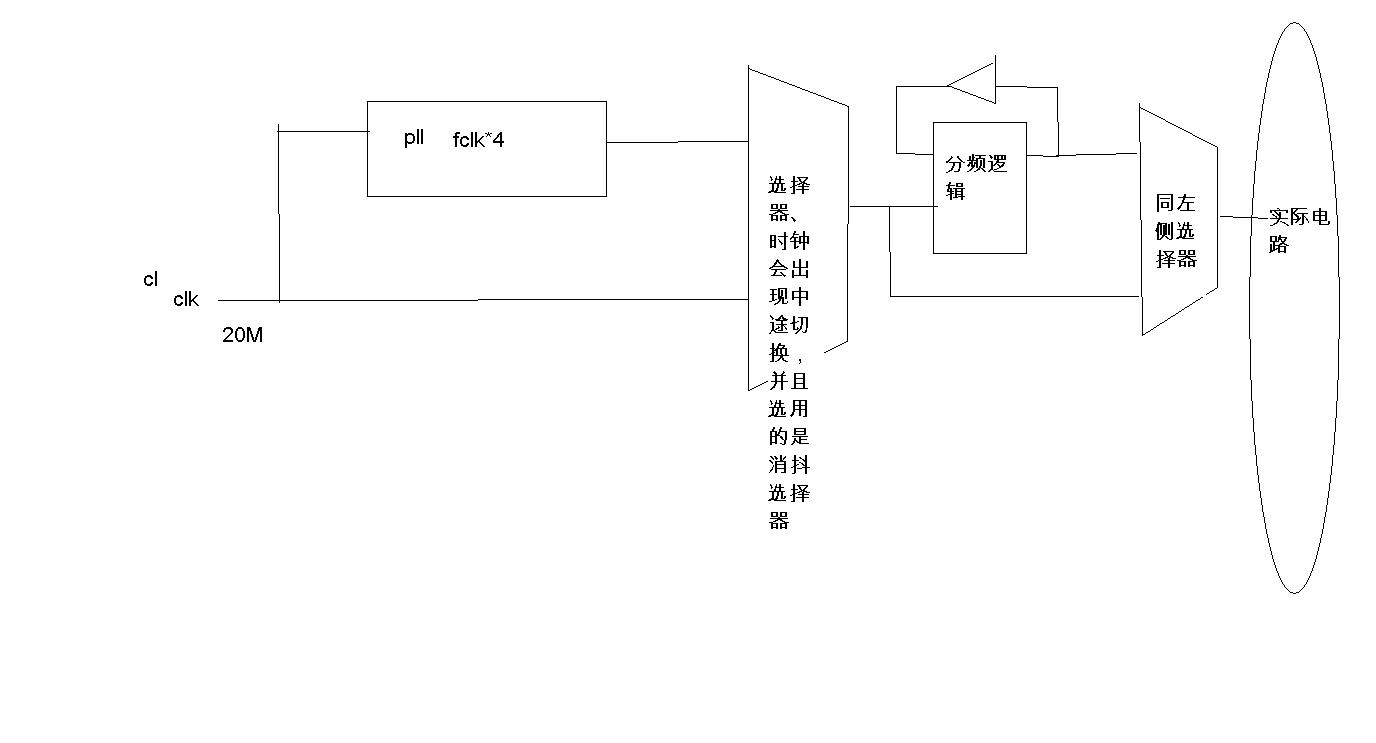

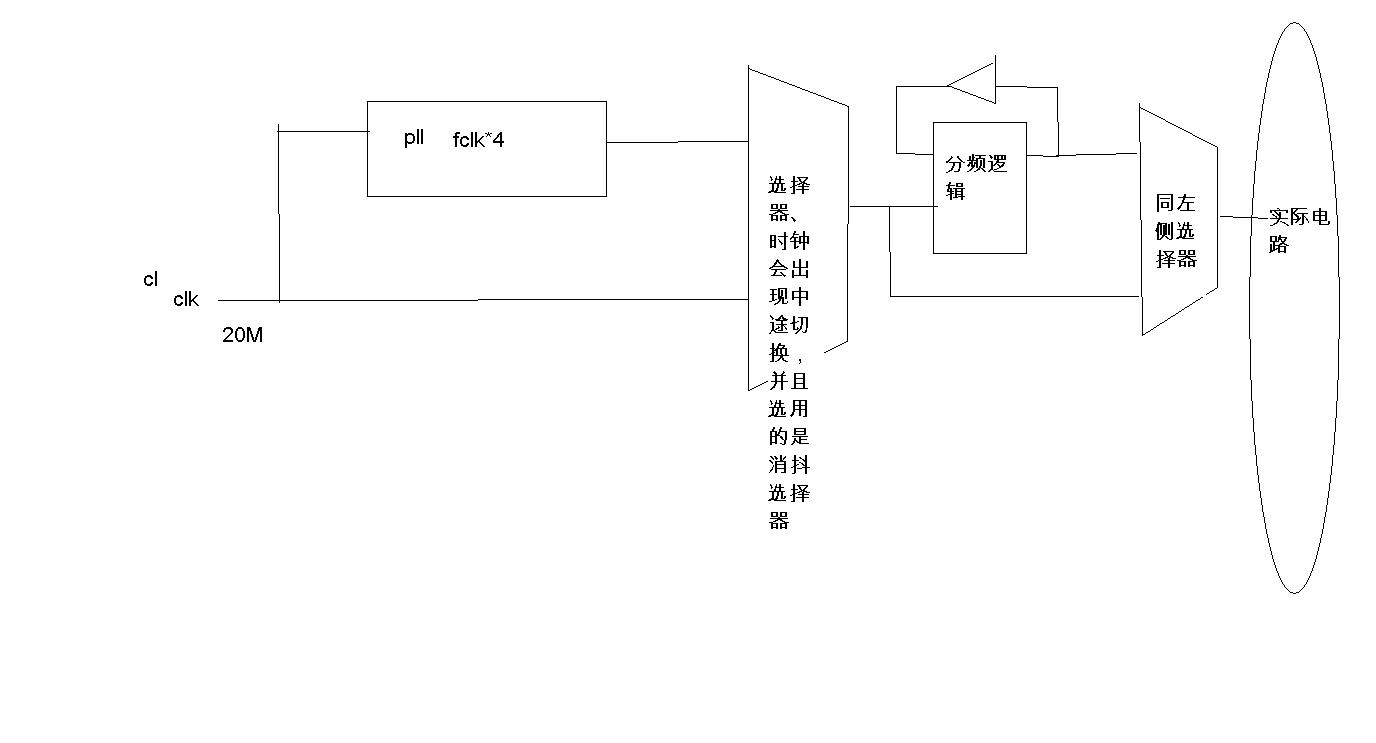

Xilinx V5芯片中实现下面的时钟管理应该怎么约束,PLL用的是V5内部的PLL,综合几百遍了,都不能过啊

综合错误是什么?选择器你用的是哪个?使用默认约束还是自己加了什么约束

不是出错,而是系统后仿不能通过,现象是通过20MHz的时钟配置寄存器不能正常配置,再有就是动态切换到pll输出以后系统就取不到正确的指令了。

由于我想让系统跑在70~80M,所以约束是我自己加的。添加了clk的周期约束,也添加了分频约束,但是由于ISE自动完成PLL输出时钟的约束,所以PLL的约束没有添加。指定的寄存器之间的传输延迟是PLL的一个周期

ISE的pll只需要约束输入,输出是pll自己去约束的。