还是一道ASIC笔试题,问verilog代码综合后的电路有何不同,仍求大神

题目是这样的

请说明下面语句综合后电路的区别

(1)

#5 a=b;

与

a= #5 b;

(2)

c=foo?a:b;

与

if(foo) c=a;

else c=b;

(1)题我答得是这样的,这两句话要实现的功能均是把b传递给a,只不过第一种写法的结果是需要在前一句代码执行完后延时5个timescale,a立即和b一致;而第二种写法使得a总是延后与b 5个timescale

(2)题我就不太清楚怎么回答了,虽然说if else 必须放在always结构里面,但是always综合出来的也可以是纯组合逻辑而不产生DFF,那样和问号选择语句功能不就一样了吗?

自己学得不扎实,求前辈指导!

说的是综合后的电路:

1)综合后应该是一样的,延迟只作用于仿真,对综合无效;

2)这个不清楚,感觉都会综合出来mux;

可能是题目我记错了,题目问的的确是“有什么不同”,我也考虑综合后电路是一样,那样就没办法回答

Gary啊,#5的语句,能综合吗,还是说综合后没有延时?我一直以为只能做测试用

延迟语句不能综合,综合时候会自动忽略;这样写主要是为了仿真的时候调整时序;

而真正的时序调整会在STA阶段实现;

以我的理解,这两个写法综合出来都是一样的

小编可以综合一下试试

1.综合工具忽略延时信息,忽略后二者代码一致,综合出来的一致

2.通常if……else……语句综合出来有优先级判断的电路,但这里只是1次判断,所以综合出来就是mux。而另一个三目运算符本来就是综合出mux。

so。我的答案如上

这么潇洒,

so……

仿真表现不一样,综合后是一样的。上面的foo为不定态时c为不定态,下面的foo为不定态时c为b。

这也算潇洒?

if else 有优先级吗?不是说优先级只能通过多个if语句才能实现吗?

第二题,貌似?:是综合出trisbuf,if else是mux的。

else if优先级?

Tim好厉害,以后还请多多指教啊

我记得以前有本书上讲,多个if语句可以实现优先级,单个if……else if……else 这样的 应该是没有优先级的,和case 语句一样。是不是和综合器有关?

Tim,有没有数字系统方面很好的书能推荐给我?

别的地方看到的答案

Q: What is the difference between:

c = foo ? a : b;

and

if (foo) c = a;

else c = b;

A: The ? merges answers if the condition is "x", so for instance if foo = 1'bx, a =

you'd get c = 'bx. On the other hand, if treats Xs or Zs as FALSE, so you'd always get c = b.

这么说,在电路设计使用if语句时候,最好是使用强等于===

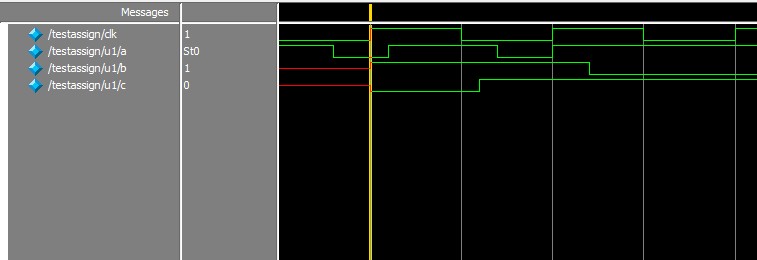

[img][/img]谁能解释下,代码为always @(a) fork b =#5a;

#5 c=a;

join

b好像不是先取a的值然后延时5个时间单位之后赋给b啊?

fork join请问什么情况下会用?还从来没用过

并行的。begin..end是串行的。我也觉得那个三目运算是三态门,是总线上用的吧。猜测。

这个语法我还是知道的,但是从来没见用过,问的问题是啥时候会用这种东西