请教,异步fifo设计时遇到一个问题

时间:10-02

整理:3721RD

点击:

代码比较简单

assign usedword=(wptr>rptr)?(wptr-rptr)full?4'hFempty?4'h016-rptr+wptr)));

always @ (posedge w_clk or posedge clear)

if(clear)

begin

wptr<=4'h0;

pwptr<=4'h0;

end

else if(!full && wr) begin

mem[wptr]<=data_in;

pwptr<=wptr;

wptr<=(&wptr)?4'h0:(wptr+1);

end

always @ (posedge r_clk or posedge clear)

if(clear)

begin

rptr<=4'h0;

prptr<=4'h0;

data_out<=8'h00;

end

else if(!empty && rd) begin

data_out<=mem[rptr];

prptr<=rptr;

rptr<=(&rptr)?4'h0:(rptr+1);

end

reg n_full=1'b0;

assign full=(wptr==rptr)?n_full:1'b0;

assign empty=(wptr==rptr)?(~n_full):1'b0;

always @ (posedge w_clk or posedge r_clk)

if(w_clk) n_full<=(wptr==prptr);

else n_full<=(wptr==prptr);

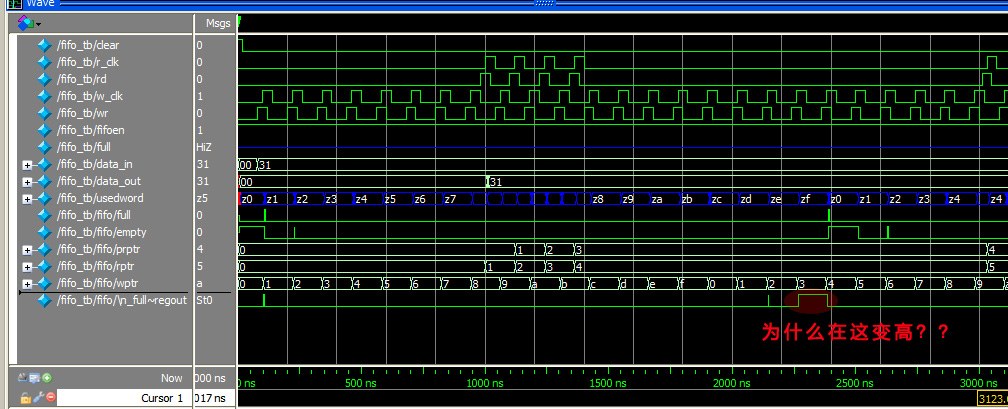

但在门级仿真时问题来多了,如图中所示

assign usedword=(wptr>rptr)?(wptr-rptr)full?4'hFempty?4'h016-rptr+wptr)));

always @ (posedge w_clk or posedge clear)

if(clear)

begin

wptr<=4'h0;

pwptr<=4'h0;

end

else if(!full && wr) begin

mem[wptr]<=data_in;

pwptr<=wptr;

wptr<=(&wptr)?4'h0:(wptr+1);

end

always @ (posedge r_clk or posedge clear)

if(clear)

begin

rptr<=4'h0;

prptr<=4'h0;

data_out<=8'h00;

end

else if(!empty && rd) begin

data_out<=mem[rptr];

prptr<=rptr;

rptr<=(&rptr)?4'h0:(rptr+1);

end

reg n_full=1'b0;

assign full=(wptr==rptr)?n_full:1'b0;

assign empty=(wptr==rptr)?(~n_full):1'b0;

always @ (posedge w_clk or posedge r_clk)

if(w_clk) n_full<=(wptr==prptr);

else n_full<=(wptr==prptr);

但在门级仿真时问题来多了,如图中所示

门级仿真

在写时钟的上升沿,wptr=2,prptr=3,此时n_full变为了高?

你的指针怎么没做跨时钟域处理?

always @ (posedge w_clk or posedge r_clk)

if(w_clk) n_full<=(wptr==prptr);

else n_full<=(wptr==prptr);

这代码啥意思?

没做跨时钟域处理:因為跨時域所以pointer在門級仿真做相互比對時會有問題

,上網看一下跨時域的的處理

1.cross clock domain, need double sync

2. use "gray code" to pass data bus