关于crc移位寄存器的设计

module serial_crc_ccitt (

clk ,

reset ,

enable ,

init ,

data_in ,

crc_out

);

//-----------Input Ports---------------

input clk ;

input reset ;

input enable ;

input init ;

input data_in ;

//-----------Output Ports---------------

output [15:0] crc_out;

//------------Internal Variables--------

reg [15:0] lfsr;

//-------------Code Start-----------------

assign crc_out = lfsr;

// Logic to CRC Calculation

always @ (posedge clk)

if (reset) begin

lfsr <= 16'hFFFF;

end else if (enable) begin

if (init) begin

lfsr <= 16'hFFFF;

end else begin

lfsr[0] <= data_in ^ lfsr[15];

lfsr[1] <= lfsr[0];

lfsr[2] <= lfsr[1];

lfsr[3] <= lfsr[2];

lfsr[4] <= lfsr[3];

lfsr[5] <= lfsr[4] ^ data_in ^ lfsr[15];// ?

lfsr[6] <= lfsr[5];

lfsr[7] <= lfsr[6];

lfsr[8] <= lfsr[7];

lfsr[9] <= lfsr[8];

lfsr[10] <= lfsr[9];

lfsr[11] <= lfsr[10];

lfsr[12] <= lfsr[11] ^ data_in ^ lfsr[15];//?

lfsr[13] <= lfsr[12];

lfsr[14] <= lfsr[13];

lfsr[15] <= lfsr[14];

end

end

endmodule

其中的两行 lfsr[5] <= lfsr[4] ^ data_in ^ lfsr[15];

lfsr[12] <= lfsr[11] ^ data_in ^ lfsr[15];

为什么lfsr[4]和lfsr[11]要和(data_in ^ lfsr[15])异或呢?不是应该和lfsr[15]异或吗?

比如如果lfsr[15]是0,就应该直接移位不做除法。但如果data_in是1,lfsr[4]和lfsr[11]就会和1异或,而不是直接移位。

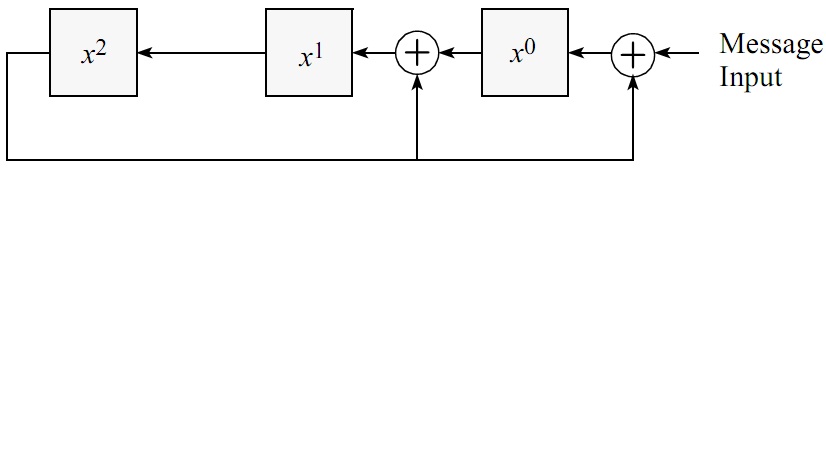

有个软件,把这种LFSR描述的很形象,有图,很直观,还可以自动生成代码和相应序列什么的

“LFSR 代码自动生成工具v1.2”

http://www.fpga.com.cn/freeip.htm#others

原理是什么呢

去看一下CRC算法的原理图就明白是怎么回事了。

如果lfsr[15]是0,就应该直接移位不做除法。但如果data_in是1,lfsr[4]和lfsr[11]就会和1异或,而不是直接移位。 这不就和crc算法不一致了吗?

是不是应该写成

always @ (posedge clk)

if (reset) begin

lfsr <= 16'hFFFF;

end else if (enable) begin

if (init) begin

lfsr <= 16'hFFFF;

end else begin

lfsr[0] <= data_in ^ lfsr[15];

lfsr[1] <= lfsr[0];

lfsr[2] <= lfsr[1];

lfsr[3] <= lfsr[2];

lfsr[4] <= lfsr[3];

lfsr[5] <= lfsr[4] ^ lfsr[15];

lfsr[6] <= lfsr[5];

lfsr[7] <= lfsr[6];

lfsr[8] <= lfsr[7];

lfsr[9] <= lfsr[8];

lfsr[10] <= lfsr[9];

lfsr[11] <= lfsr[10];

lfsr[12] <= lfsr[11] ^ lfsr[15];

lfsr[13] <= lfsr[12];

lfsr[14] <= lfsr[13];

lfsr[15] <= lfsr[14];

end

end

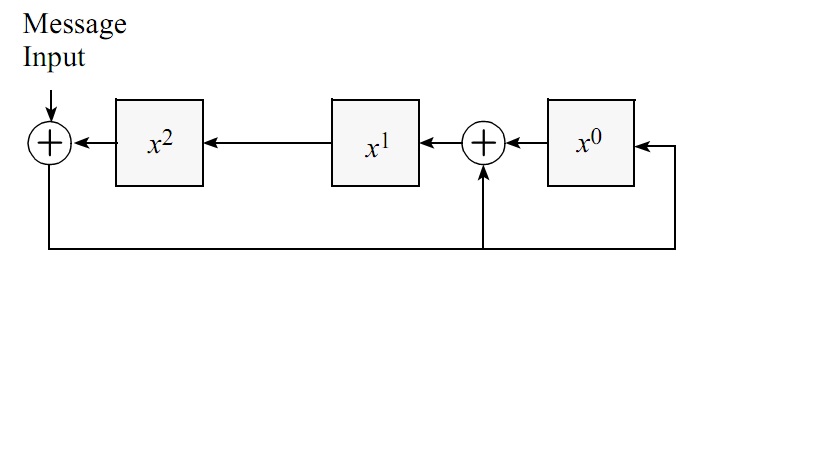

看一下CRC的多项试,把那个抽头的图话出来就可以理解了

G=x3+x+1

这两种结构等价吗

假设计算CRC16,第一个图对应的输入数据应该是{data_in,16'b0}串行输入,第二个图对应的输入数据就是data_in的串行输入,第一个原理好明白,但是第二个还没搞清楚,这两个图都是正确的,但是输入数据不同