有关三分频电路

我觉得没那么复杂,简单的计数就可以了,

以下是我写的代码,请各位高手看看对不对,相比网上那些复杂的方法是不是有缺陷

module div3(reset,clk_in,clk_out

);

input clk_in,reset;

output clk_out;

wire clk_out;

integer n1;

reg clk1;

always @(clk_in or negedge reset)

begin

if (!reset)

begin

n1=2;

clk1<=1'b0;

end

else if (n1==2)

begin

n1=0;

clk1<=~clk1;

end

else

begin

n1=n1+1;

clk1<=clk1;

end

end

assign clk_out= clk1;

endmodule

可能别人设计的是占空比50%的吧,所以会复杂点。

我这个也是占空比为50%的

仿真了吗? 看起来好像是6分频

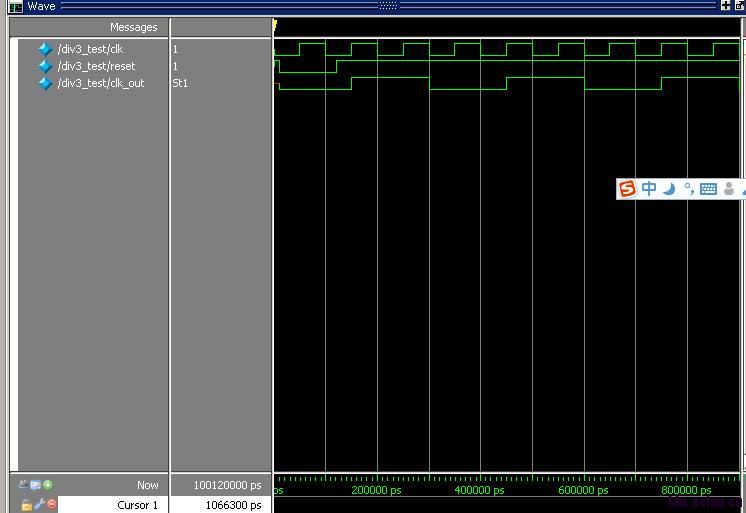

这是仿真图

你看到的很复杂的三分频电路是什么样的?

不是用的上升沿下降沿双判断的方法吗?

问题是你这个

always @(clk_in or negedge reset)

用时钟双边沿,在FPGA内无法实现。

有人说ASIC有对应器件。

但是在项目中无法用FPGA验证、时序分析和后端都会被这个东西堵一下,还是不要用了。

这个既用边缘触发又用电平触发,在FPGA上是不能实现的,尽管你的仿真是对的

感觉不太对

小编是学生?

你写的这个东西只能跑跑仿真,是不能综合成硬件的。

又来一个程序员....

现在国内设计电路的孩子都以为自己在做软件编程么....

非同步设计,上下沿加电平触发,又是阻塞赋值又是非阻塞赋值的。

这样子设计的东西基本没实用价值。

明白了,多谢各位了

赞成楼上的,既有电平,又有边沿。怎么实现嘞?

想法不错哦······

实际Run不起来的,同学

同样学生,学习了

小编的应该是6分频的吧?别人的应该是三个周期变为一个周期,也就是输入clk的1.5个周期输出clk变化一次……所以会复杂一些,而如果要实现偶数次分频用HDL是很好实现的。

lz,只能说你还停留在看结果的层次。

你这个是能在FPGA和ASIC实现么?

所以说verilog害人啊,还没懂数字电路的就看verilog,写出来的东西真是千奇百怪啊。

我是学VHDL的,看不懂这个呀!

你这个其实就已经采用了双边沿采样,posedge clk_in 和negedge clk_in,就算能够综合,门级电路也是一样的复杂

另外,是不提倡你这种电平采样的写法的!