always块中的敏感变量

always @(a or b or sel) begin

case(sel)

2'b00 : d <= a;

2'b01 : d <= b;

2'b10 : d <= c;

default : d <= 1'b0;

endcase

end

c没有被写入到敏感变量中,这样会出现锁存器吗?

问题相当严重

这个就是latch

推荐使用always @(*) 让系统去主动推断 当然是verilog-2011才可以哈

但是我刚用quartus 和 ISE 测试了,没有latch啊

当然没有latch,只是仿真结果和上板的结果不一样 。

会造成前仿和后仿不一致。

跑一下formality就能查出这些问题的。

建议用always @*。现在工具对verilog2001已经支持得很好了。

可以仿真试试这种情况的输出:

sel一直为2‘b10,然后变化C的值,看看输出结果,是不是预期的

会造成仿真结果和预期的不一致,除此之外,综合上不会有任何问题,稍微新一点的工具都足够聪明,能找到正确的敏感表。

就是说在综合之后观察RTL结构图,是看不到latch的;但是下板之后是有latch的吗?

您的意思就是说 实际上是产生了锁存器的吗?

您所谓的仿真结果和预期结果不一致,仿真指的是前仿还是后仿,预期结果是指的下板后的结果吗?

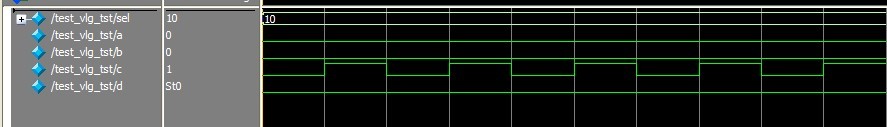

我按照您所说的做了下功能仿真,结果显示是错误的,always块没有被触发,稍后我再做下后仿试试。[attach]466859[/attach]

很有可能会出现的。

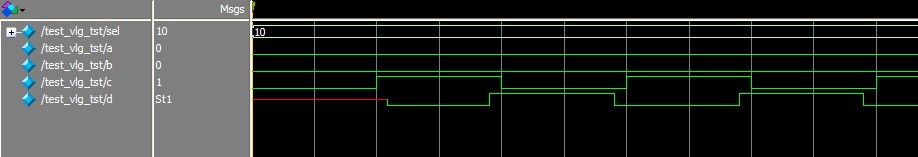

我做了一下时序仿真,下面是波形图,d和C之间的延迟大概有9ns,我不知道是否有锁存器生成。我用的quartus ii 10.0综合的。

你这功能仿真按照你的code就是对的,因为没有a,b,sel确实都没有变,always不会被触发

这种问题其实不用纠结,宁可多写敏感变量(一般通配所有变量),也不要写漏掉

不是。你这个能正确地综合出一个选择器,不会出锁存。

比如说,sel=2'b10的时候,如果c发生了变化,后仿的时候,如果d会跟着变,但你前仿就不会变。

绝对latch

主要是前仿。后仿应当问题不大。

懂了,谢谢你~!

哦,明白了。15L里面我贴了一个后仿的图,为什么它的延迟会有9ns这多大呢?

敏感列表不全,就会出现warning,于是我为了消除warning,把敏感列表给加全了……