请教MMCM时钟锁定的问题

时间:10-02

整理:3721RD

点击:

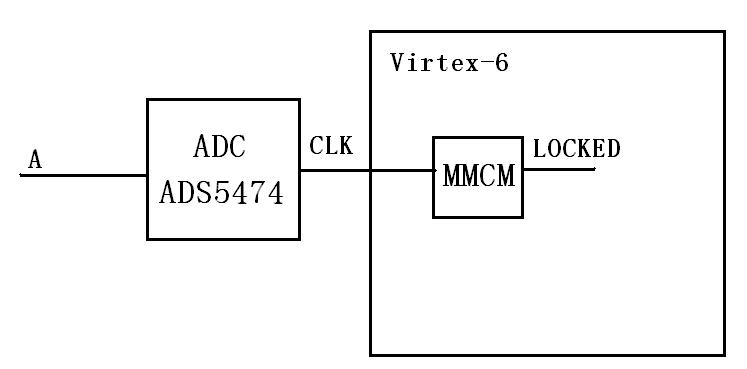

如上图,在A点给ADC输入一个时钟,ADC的输出时钟给MMCM模块输入。

问题:当断掉时钟A后,LOCKED信号仍然指示锁定。

个人觉得不会。LOCKED会由高变低。这个可以仿真看出来。

是会为低的,

另外,注意下复位信号的产生,要是复位信号是为经过此时钟打拍后置位和释放,而此复位信号又控制MMCM的复位,可能会限入死循环,这个要避免。

复位信号由外部供给,异步复位嘛。

实际情况测出来就是这样子,会不会ADC时钟停掉后内部锁相环还在工作。比如我设置MMCM的输入时钟为200MHz,但实测出来当输入时钟25MHz以上MMCM-LOCKED都还为高。或者是软件版本问题?用的ISE13.2的

你应该好好看看datasheet 在时钟断掉的时候,locked仍然确实为高。因为locked被锁存的,所以在V4系列dcm的手册里写的很明确,具体的状态是看stauts输出端的,至于V6,暂时没有这样用到。你可以查一查