新手问个低级问题--关于流水线中的寄存器模块的问题,谢谢

时间:10-02

整理:3721RD

点击:

在CPU设计中,寄存器模块通常都是用的时序器件,这样的话不是相当于在流水线中间插入了一级吗?

在CPU设计中,寄存器模块通常都是用的时序器件,这样的话不是相当于在流水线中间插入了一级吗?

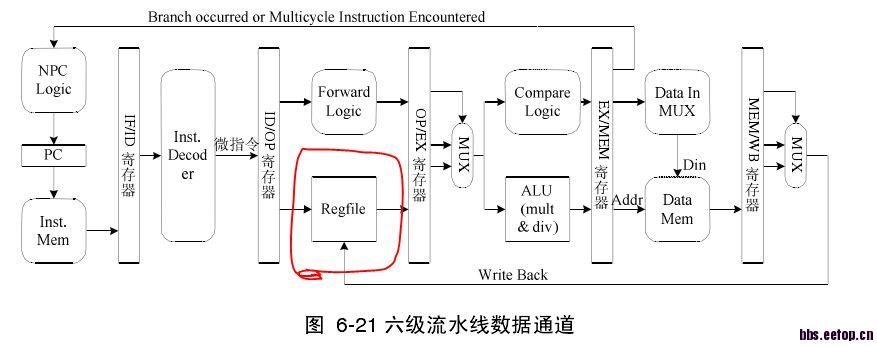

如图所示,图中的Regfile就是是时序器件。

补充说明一下:

举个MIPS五级流水线的例子,IF,ID,EX,MEM,WB

时钟1上升沿时,在ID级输出访问的寄存器地址,但是由于寄存器模块是时序的(我的理解是:时钟上升沿输出,如下面代码所示),到时钟2的上升沿,才会输出结果;

而ID/EX寄存器又是时序的;

这样的话。ID级访问寄存器,访问结果不是需要两个时钟才能输出到EX段吗?

而且看到好多代码中都是这样写的(OR1200 、ucore )。求指导。谢谢。

always @(posedge clk_i or posedge rst_i)

begin

if(rst_i)

begin:INITIAL_SECTION

integer i;

for(i=0;i<32;i=i+1) mem <= 32'b0;

end

else begin

douta <= ena?mem[porta]:32'b0;

doutb <= enb?mem[portb]:32'b0;

if (enc && portc != 0)

begin

mem[portc] <= dinc;

end

end

end

在CPU设计中,寄存器模块通常都是用的时序器件,这样的话不是相当于在流水线中间插入了一级吗?

如图所示,图中的Regfile就是是时序器件。

补充说明一下:

举个MIPS五级流水线的例子,IF,ID,EX,MEM,WB

时钟1上升沿时,在ID级输出访问的寄存器地址,但是由于寄存器模块是时序的(我的理解是:时钟上升沿输出,如下面代码所示),到时钟2的上升沿,才会输出结果;

而ID/EX寄存器又是时序的;

这样的话。ID级访问寄存器,访问结果不是需要两个时钟才能输出到EX段吗?

而且看到好多代码中都是这样写的(OR1200 、ucore )。求指导。谢谢。

always @(posedge clk_i or posedge rst_i)

begin

if(rst_i)

begin:INITIAL_SECTION

integer i;

for(i=0;i<32;i=i+1) mem <= 32'b0;

end

else begin

douta <= ena?mem[porta]:32'b0;

doutb <= enb?mem[portb]:32'b0;

if (enc && portc != 0)

begin

mem[portc] <= dinc;

end

end

end

流水线就是靠寄存器来实现的,只是在第一个时钟上升沿慢一个时钟周期,以后再读寄存器时,同时也在往里写数据。以此类推,总的时间减少了

寄存器存的是上一个cycle的值, 2号cycle 的输入在3号cycle才能输出

学习了。