请教用verilog给存储器建模的问题

时间:10-02

整理:3721RD

点击:

我想建模一个类似于个指令存储器差不多的内存,参考了一些资料,写出以下代码

我是想给Imemory里的每个字都赋值,但是仿真结果出来时Imemory里面什么值都没有啊

我用shu去读Imemory里的每个字,读出来的结果都是xxxxxxxx。

请教一下这个verilog错了吗?

如果错了,请问要建立一个类此于存储器的东西如何写verilog代码啊?

谢谢!

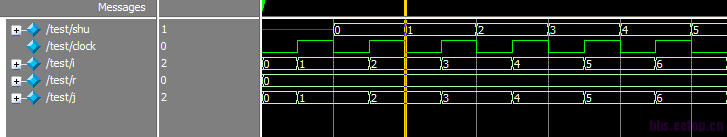

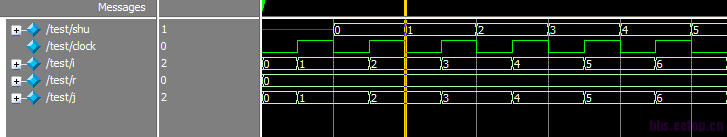

下图是修改后的成功仿真图

你源程序的问题在于

连续赋值语句

assign shu = Imemory是在数据i的值有变化时即刻将值赋给端口shu,而实际的写入存储器是在时钟的上升沿,也就是说当i变化时,并没有有效的数据。所以读出有问题。

我是想给Imemory里的每个字都赋值,但是仿真结果出来时Imemory里面什么值都没有啊

我用shu去读Imemory里的每个字,读出来的结果都是xxxxxxxx。

请教一下这个verilog错了吗?

如果错了,请问要建立一个类此于存储器的东西如何写verilog代码啊?

谢谢!

memory 赋初值?

看下 $readmemh 或者 $readmemb 吧

如果只是赋初值,用$readmemh 或者 $readmemb

读出来是xxxx,应该是因为单元没写入(非阻塞赋值)。

存储器赋值不应该是那样赋值吧!不应该是一个一个的来赋值么

我觉得你这个完全可以用IP核来实现啊,如果是想赋初值,IP核生成的时候可以用一个COE文件来说明的。不知道你用的时哪个软件

初学,共同关注

恩,是想给寄存器堆赋初值,您的方法我看到过,我会尝试的。

哦,那就是说我写的语句没有给寄存器堆赋值的咯,感谢您的解答。

求问除了readmemh和readmemb这个方法外,类似于我这种给寄存器堆一个一个寄存器赋值过去的语句有吗?谢谢

我写的是类似于寄存器堆的东西啊,只有一次性给寄存器堆写入数据吗?没有给寄存器堆一个个寄存器写入数据的方法吗?

我仿真用的是synopsys的VCS,还没接触过存储器的IP,我暂时只想建模一个类似于存储器的东西,用于仿真我的整个带存储器的电路。

但好像就是因为这个存储器的语句写的有问题,导致我整个电路无法仿真

呵呵,我也是新手

不知道可不可以把 shu定义成reg 然后放到always块里面去?

- module test(shu);

- output reg [31:0] shu;

- reg clock;

- reg [31:0] i,r;

- reg [9:0] j;

- reg [31:0] Imemory[0:1023];

- initial begin

- clock <= 0;

- i <= 32'h0;

- r <= 32'h0;

- j <= 32'h0;

- end

- always @(negedge clock)

- shu <= Imemory[i-1];

- always @(posedge clock)

- begin

- Imemory[j] <= i;

- i <= i+1;

- j <= j+1;

- end

- always

- begin

- #1 clock <= ~clock;

- end

- endmodule

下图是修改后的成功仿真图

你源程序的问题在于

连续赋值语句

assign shu = Imemory是在数据i的值有变化时即刻将值赋给端口shu,而实际的写入存储器是在时钟的上升沿,也就是说当i变化时,并没有有效的数据。所以读出有问题。

非常感谢您的回答,我已经成功赋值了,我犯了很低级的错误,呵呵

至于您写的第二行的语法不知道是verilog的版本,我在VCS上仿真无法通过,不过我修改成其他的类型就好了

非常感谢!

可以的,您说的方法是可行的。谢谢