关于的问题 inputdeay

时间:10-02

整理:3721RD

点击:

关于的问题 inputdeay

一个外部的传感器,电平的转化的参数

Output Rise time :Tr=1.0 us (平均值)

output falling time :Tf=0.3 us (平均值)

将这个传感器的输出信号输入到FPGA,作为FPGA芯片的输入信号;

FPGA内部时钟速度为100M;

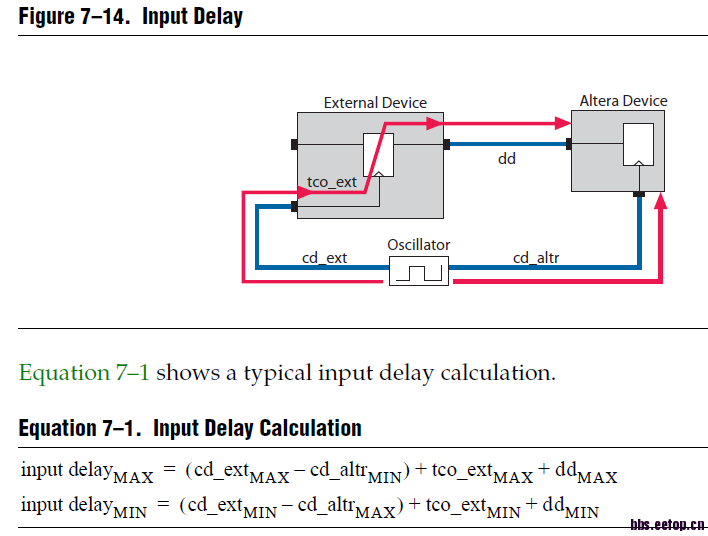

那么在设置input delay 的时候,怎么设置以下的参数呢?

cd_extMAX

cd_altrMIN

tco_extMAX

ddMAX

怎么进行估计?通过观察PCB的走线?还是在仿真调试的时候,慢慢修改

以前对波形要求不严格的时候,只是随意的设置了一下,

现在望大家指点一下。

一个外部的传感器,电平的转化的参数

Output Rise time :Tr=1.0 us (平均值)

output falling time :Tf=0.3 us (平均值)

将这个传感器的输出信号输入到FPGA,作为FPGA芯片的输入信号;

FPGA内部时钟速度为100M;

那么在设置input delay 的时候,怎么设置以下的参数呢?

cd_extMAX

cd_altrMIN

tco_extMAX

ddMAX

怎么进行估计?通过观察PCB的走线?还是在仿真调试的时候,慢慢修改

以前对波形要求不严格的时候,只是随意的设置了一下,

现在望大家指点一下。

随便设,或者直接设成1ns/2ns之类,以满足你FPGA片内时序关系为主,

因为这个外来的信号变化太慢了(都快一百倍了),不用去CARE采错的事情,就算有,关系也不大,直接把进来的信号打二拍使用即可。

虽然不明白,但感觉楼上说的挺好的。

好的,谢谢

LZ画的那个时序图,一个芯片的输出到另一个芯片的输入,T_co + T_delay+ T_su - T_clk_delay < T, 这个公式是没错,一般情况下我们要满足,但指的是这两块芯片的数据速率是同一个时钟变化的,比如都是100 MHZ,那得< T 10ns,

或者如果前面芯片的输出如果是个快速脉冲,10ns宽度的脉冲的话,那速度的变化也是100 MHZ了,也要满足上面的公式,要不然就采不到了。

但现在前端芯片的输出是高1us, 低0.3 us, 也就是最快的数据变化率也是0.3 us,相当于速度3.3 KHZ,远低于后端的100MHZ,那后面时钟去采这个数据的时候,多采一个周期或少采一个周期,也就是10 ns的误差而已,那看一下误差, 也就是10 ns/0.3us,3%而已, 如果这个信号仅仅是做控制使用的,那就不需要CARE,反正要控制的高、低信号都会来,也不指望这个信号来的时间和长短非常精确。 如果是要用到累积效应的,比如做MPW之类使用,高的时候要相加,低的时候保持不动,最后取平均值的那种,那这个要注意下。再来计算来真正的误差率10 ns/(1us+0.3us),1%而已,也是相对没有啥关系的。

受教了,谢谢