关于乘法器输出

时间:10-02

整理:3721RD

点击:

请问为什么可以这样,这样的话误差不是非常的大吗?

这个没办法,位数不够,总要丢掉点什么。

只是个取舍问题

截取数据从高位开始,可能高两位没用。

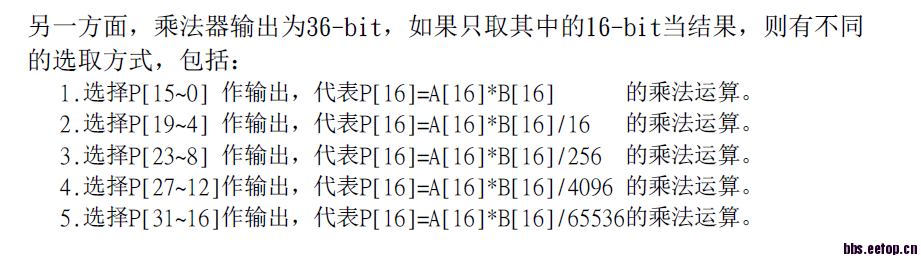

这个要从算法上说起,看你怎么对待运算精度了,如果你的输入的A和B都是小数的话,这样在实现乘法的时候,你先放大,乘完后再截位,这样本身的精度是没有损失的,如果两个数都是整数,若输出因为有位宽限制,这样你截位的时候可要注意了,这要和你的数的大小有关系了,很可能高位全是符号位,这样你要选择低位,而不能从高位截取。

这就是截短误差,难免的

要考虑输入数据的范围,否则可能会溢出。另外,这样是直接截位,要想提高精度的话,需要四舍五入在乘法器外面截位。

我回复是来看头像效果的 ,不好意思