求教带斩波的△∑ADC的降采样滤波器的设计

时间:10-02

整理:3721RD

点击:

大侠们好:

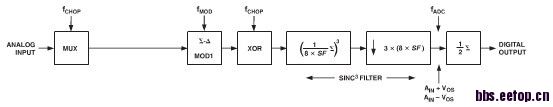

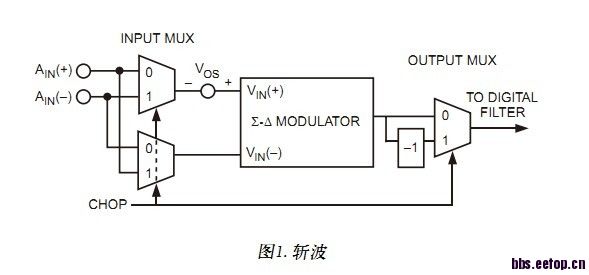

我目前在做一个滤波器,是用于斩波ADC的降采样滤波器。系统架构大致如下图:第一个图是ADC的系统框图,第二个是斩波作用时的调制器框图、。

问题1:经过斩波输出的调制器数据是否可以直接用于FFT分析,来评价调制器性能?

问题2:按我的理解,调制器在输出时,数据已经被斩回来了,调制器输出数据已完全可用,那么为什么还要用sinc3进行3倍的降采样来消除建立时间内的数据呢?

还望有人解答。谢谢

我目前在做一个滤波器,是用于斩波ADC的降采样滤波器。系统架构大致如下图:第一个图是ADC的系统框图,第二个是斩波作用时的调制器框图、。

问题1:经过斩波输出的调制器数据是否可以直接用于FFT分析,来评价调制器性能?

问题2:按我的理解,调制器在输出时,数据已经被斩回来了,调制器输出数据已完全可用,那么为什么还要用sinc3进行3倍的降采样来消除建立时间内的数据呢?

还望有人解答。谢谢

都下班了吗?求助啊