关于TimeQuest设置多周期路径失败

时间:10-02

整理:3721RD

点击:

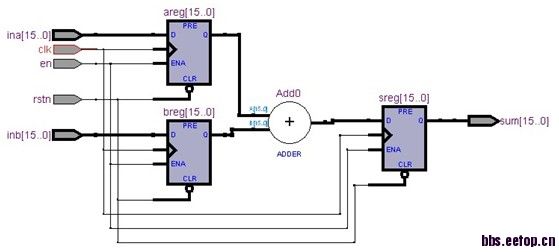

向大家请教一个问题,我在TimeQuest里设置多周期路径,按照如下RTL来设置

我写的约束如下(我设置的clk周期为2ns,设置每2个周期采样一次)

set_multicycle_path -setup -end -from [get_pins {areg*|clk breg*|clk}] -to [get_pins {sreg*|datain}] 2

set_multicycle_path -hold -end -from [get_pins {areg*|clk breg*|clk}] -to [get_pins {sreg*|datain}] 1

可是在TimeQuest分析的时候,发现这些设置有些生效了,有些却还是无效

红色部分中Relationship中仍为2.000,说明他仍然是单周期采样,但是黑色部分为4.000明显已经生效了,

为什么一部分生效一部分失效呢?

图挂了...

这样啊,那我在发一遍

向大家请教一个问题,我在TimeQuest里设置多周期路径,按照如下RTL来设置

我写的约束如下(我设置的clk周期为2ns,设置每2个周期采样一次)

set_multicycle_path -setup -end -from [get_pins {areg*|clk breg*|clk}] -to [get_pins {sreg*|datain}] 2

set_multicycle_path -hold -end -from [get_pins {areg*|clk breg*|clk}] -to [get_pins {sreg*|datain}] 1

可是在TimeQuest分析的时候,发现这些设置有些生效了,有些却还是无效

红色部分中Relationship中仍为2.000,说明他仍然是单周期采样,但是黑色部分为4.000明显已经生效了,

为什么一部分生效一部分失效呢?我用的是Quartus 9.1

试试 -from [get_registers {areg* breg*}] -to [get_registers {sreg*}]

看来是软件的bug,我换了quartus 11.1版本之后就没有问题了。

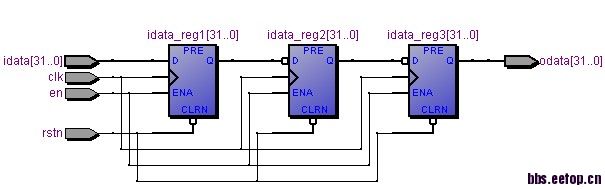

现在还有另外一个问题,我看的很多资料,关于多周期路径的设置都是基于两级寄存器的,比如我上面(areg、breg)为第一级,sreg为第二级,问题是,如果有很多级的话,比如下图

共有三级寄存器,其中每两级之间采样周期间隔都是2,我写的约束如下,已经验证没有问题

set_multicycle_path -setup -end -from [get_pins {idata_reg1*|clk}] -to [get_pins {idata_reg2*|datain}] 2

set_multicycle_path -hold -end -from [get_pins {idata_reg1*|clk}] -to [get_pins {idata_reg2*|datain}] 1

set_multicycle_path -setup -end -from [get_pins {idata_reg2*|clk}] -to [get_pins {idata_reg3*|datain}] 2

set_multicycle_path -hold -end -from [get_pins {idata_reg2*|clk}] -to [get_pins {idata_reg3*|datain}] 1

有没有什么办法,能一条语句就能将三级寄存器都约束,因为如果有很多级的话,两级两级的写效率实在太低