关于signalTap采样时钟的疑问

可以用锁相环输出的100M时钟作为signaltap的采样钟。

而且50M的系统时钟是不能采样100M钟下的信号的,这样相当于慢时钟采样快时钟,signaltap中的结果将是不正确的。

2# sirius.yuan

谢谢!这也是我要用100M采样时钟的原因。然而在添加采样时钟的node finder中我根本找不到100M的时钟信号。

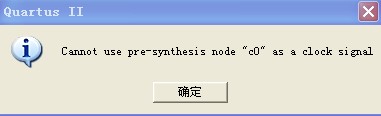

我锁相环生成了三路100M的时钟:c0、c1、c2。在signalTap II:post-fitting信号列表中找不到这三个信号,而在entity【all names】信号列表中有显示,如图1所示。选择其中一个后,提示图二中的错误,根本没法添加。请问要怎么才能使用100M的采样时钟呢?

图1

图2

在signalTap II:pre-synthesis信号列表中找找试试看

肯定是可以使用PLL的输出的,这个我试过,在Node里查找。

4# sirius.yuan

在pre-synthesis信号列表中有这三个信号,添加后同样弹出我上面图中所示的提示————还是无法使用啊,是不是还要在别的什么地方添加设置啊5# spritez

不知道你用时在node finder中选的时钟信号前面的标志是R、I或者是C呢?我发现符号是C的信号就不能用,我的几个100M时钟信号前的标志都是c刚试了一下,我的就是C的,可以加入。

8# spritez

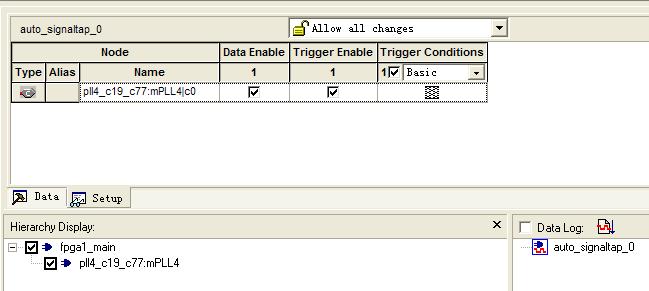

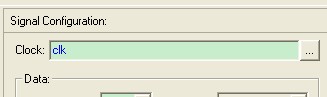

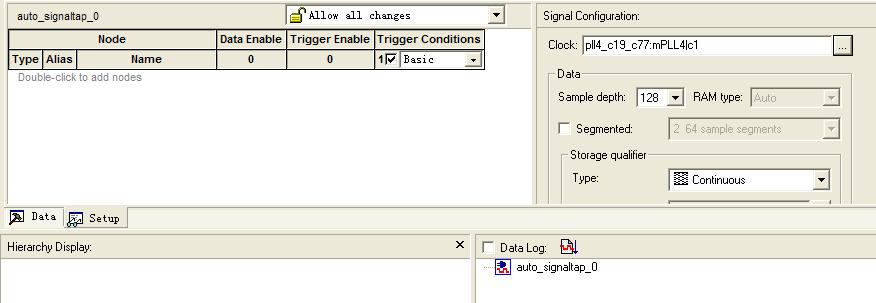

我想加的是锁相环输出的100M时钟作为采样时钟,采样时钟的设置位置应该是在下面图中的位置吧?你图中选的是要观察的信号我觉得。我在某些文献中看到说signalTap是不能观察锁相环的输出信号的,所以加进去了估计也观察不到。

没问题,我都用过了,是这样吗?

会不会是这个芯片系列本身不支持呢?

10# spritez

行了,谢谢!我今天也遇到了这个问题,我遇到的问题是系统采数出错,在时钟选择的时候,所以我想看看,当SEL变化时,时钟切换时什么样的,,,可惜锁相环的始终怎么都家不进去,,,找不找不到,我试了所有的选项都不行

盼高人来解释

好像signaltap不支持PLL的测试

谢谢 分享谢谢 分享

可以的!

最简单的方法,就是你把100M时钟做成一个输出端口就好了,这样在找引脚的时候选择pin:all就能找到那个时钟端口了。

锁相环的输出时钟在signaltap中是无法观测的。

逻辑分析器不可测试的信号包括:逻辑单元的进位信号、PLL的时钟输出、JTAG引脚信号、LVDS(低压差分)信号。