ASIC和FPGA/CPLD的区别

时间:10-02

整理:3721RD

点击:

随着数字IC的发展,数字系统的实现主要选择2种器件:即可编程逻辑器件(PLD)和专用集成电路(ASIC)。其中PLD又可以分为FPGA(Field Programmable Gate Array)和CPLD(Complex Programmable Logic Device)。现在来梳理一下FPGA/CPLD和ASIC的区别。

一、FPGA/CPLD

FPGA/CPLD同属于PLD家族,是一种半定制器件,所谓半定制,即所提供的器件已经做好各种逻辑资源,用户只需要根据自己的需求对器件内的资源进行编程连接就可实现相应的功能,而且可以反复修改,反复编程,直到满足用户需求。FPGA使用方便,灵活,开发效率高,成本低,风险小。

FPGA/CPLD的设计流程包括:设计输入、综合、布局布线、仿真和编程配置。CPLD是基于EEPROM工艺的非易失性结构,针对它的下载成为编程(Program),FPGA是基于SRAM工艺结构,针对它的下载称为配置。

二、ASIC

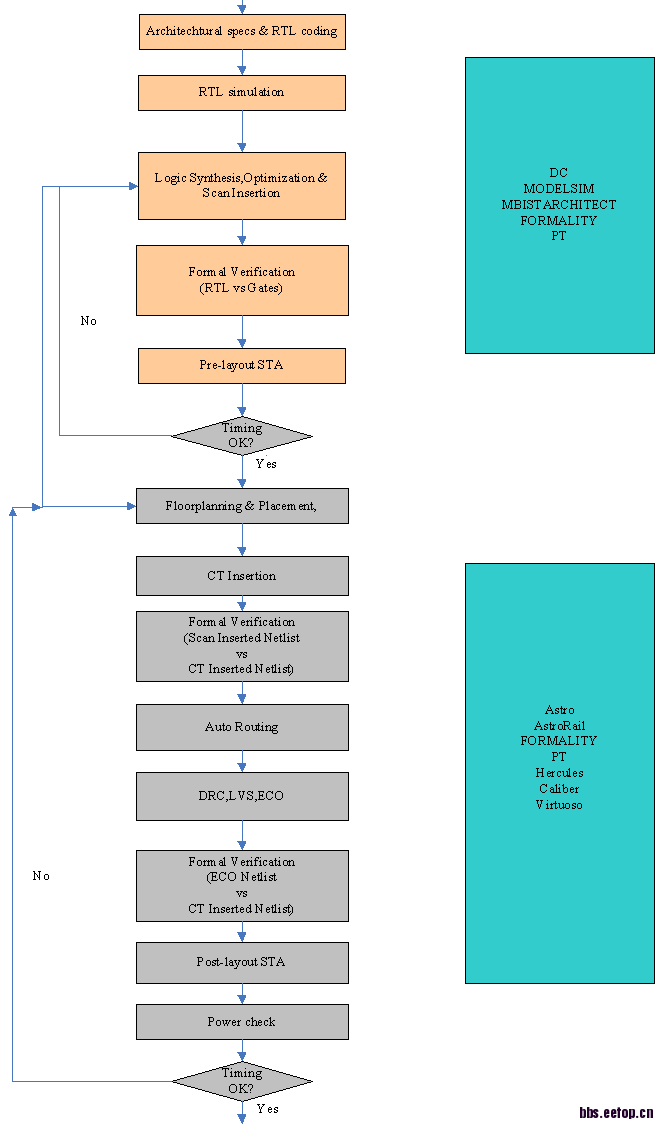

ASIC是一种全定制的方式的设计实现,它在最底层,即物理版图级实现设计。因此,ASIC可以获得比FPGA/CPLD更高速度,更低功耗和面积更小的设计。在版图设计时,设计者需手工设计版图并精心布局布线,以获得最佳性能和最小面积。在版图设计完成后,还需进行一系列检查验证,包括,设计规则检查、电学规则检查、连接性检查、版图和电路图一致性检查等,全部通过后,才可以将得到的标准格式的版图文件(CIF, GDSII)交与半导体厂家进行流片。相对FPGA/CPLD,ASIC的设计流程更长,分为前端设计和后端设计。前端设计以生成可以布局布线的网表(Netlist)为终点(FPGA到此就可以编程下载);后端设计以生成可以送到foundry进行流片的版图文件(GDSII)为终点。

参考《数字系统设计与Verilog HDL(第四版)》 王金明编著

“数字IC设计流程”

谢谢小编,学习了。

欢迎指正,互相交流学习。

温习温习

谢谢小编,学习

学习中。

不错啊!