modelsim 后仿 信号全都是不定态

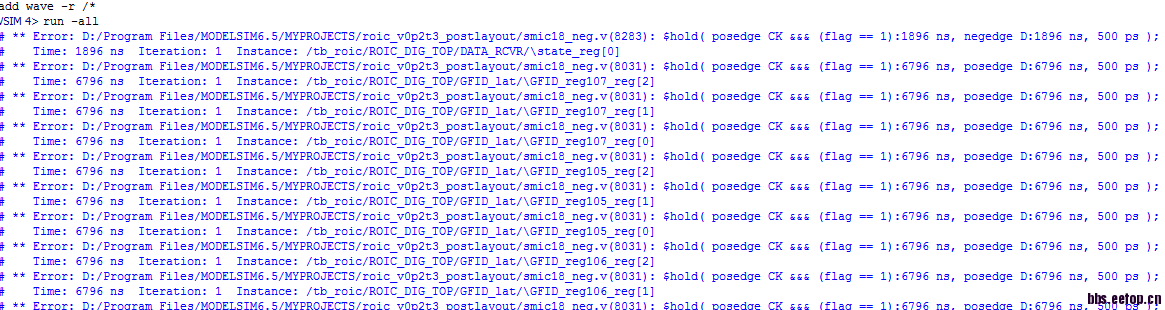

我在做完PR之后,用formality做了形势验证,顺利通过,本来应该先将astro导出的网表去抽spef做sta的,但是先直接用astro导出的sdf拿来做后仿了,想先看看大致的仿真时序,但是用modelsim加入sdf和库文件之后,仿真结果都是不定态,而且run的时候似乎有error(见下图),求高人指点:[attachimg]442478

有没有人知道在跑仿真的时候,出现这个error是什么原因造成的啊?我已经焦头烂额了

你的GFID_reg保持时间有问题,理论上应该是500us的,不知道你仿真的时候是怎么设置的

你试着让信号延迟或者提前600us左右看看

谢谢你的回复,但是这个事内部信号啊,而且我是反标了延时信息的,还有就是我用PT做layout后的STA,hold是大于2个ns的(这是我故意多留的),但是到后仿还会出现hold不满足,真是闹不明白啊!

这种error表示你的设计时序有问题。你去STA下。

我之前也遇到过这个问题。后仿真不能有error,有error一般就是时序问题。我后来把slack加大了就后仿就OK了。STA ok并不表示后仿真OK。

恩,我sta报出来的不仅没有时序违例,而起我给余量也很大,setup超过5ns,hold大于1ns,我试过两种情况,一种是在tb中插入延时信息——后仿还是有部分信号不对,另一种就是原封不动的用前仿的tb,只反标延时信息,加载工艺库,这种情况下有可能报时序错误,还有就是什么信号都不出!

所以我想是不是tb中给各个输入激励应该设置不同的延时信息,模拟实际情况!

还有一种可能就是你的TEST激励代码的问题了。你查查看

前仿没有没有问题,说明我给的激励波形是对的,只是时序上还要调整,对吧?

视乎是这样

看看这个吧,http://www.eetop.cn/blog/269296/viewspace-24785.html;你的问题与ncverilog仿真应该类似,应该可以用相同的参数。

恩,谢谢,我现在是在后仿真中设置了合适的input delay之后,就没有X了

恩,如果是在modelsim中,怎么设置呢,我没有用过脚本模式

我自己也没怎么用过modelsim,而且只会使用脚本格式。使用do文件很简单方便还能保存波形。不过我记得图形界面里应该有个compile option设置,你在那个里面填上+no_notifier试试。

没有试过,我现在是先产生理想的激励信号,然后在给进DUT时候加上一定的延迟时间,然后凡标sdf,编译,仿真,是可以出信号的,结果也与预期相同,只是有些地方信号到达时间不一致出现了一些小小的毛刺,应该没有问题了吧?哈哈

嗯,应该是可以的。