怎样用VERILOG HDL编写HDB3 译码电路

时间:10-02

整理:3721RD

点击:

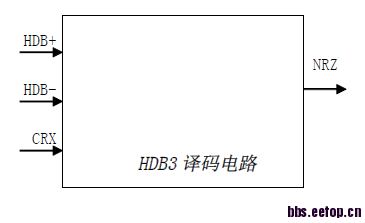

3:HDB3 译码电路

HDB3 译码电路完成编码的反变换,关键之处是检出破坏点,取消“取代节”,即将

“000V”或“B00V”还原成“0000”,其管腿框图如下

4:要求:

工作速率为50kb/s~10Mb/s(符合CCITT G.703 建议)

这里取时钟频率=2M,信号速率=2M。

用VERILOG HDL 进行电路描述,并写出测试文件。电路仿真结果正确。

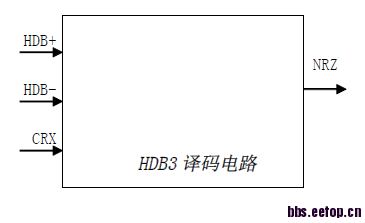

HDB3 译码电路完成编码的反变换,关键之处是检出破坏点,取消“取代节”,即将

“000V”或“B00V”还原成“0000”,其管腿框图如下

4:要求:

工作速率为50kb/s~10Mb/s(符合CCITT G.703 建议)

这里取时钟频率=2M,信号速率=2M。

用VERILOG HDL 进行电路描述,并写出测试文件。电路仿真结果正确。

周二就要验收了,各位大大帮帮忙啊。

代码,注释。

给多少钱呢 没钱别扯那没用的