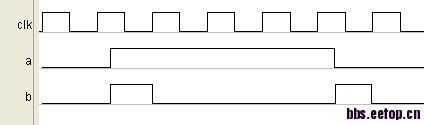

2011年9月3日MTK硬件部门的笔试题:根据时序图写verilog代码

根据时序图写verilog代码,已知时钟信号clk和输入信号a,要获得如图所示的b,应该怎么编写verilog代码?

一、分析:

1、信号a应该是随机给的,b相对于a和clk的规律应该是:一般情况下,b为低电平,当a出现上跳沿和下跳沿的时候,b变成高电平;若b是高电平且是clk的上跳沿的时候,b变成低电平。

2、敏感列表的内容包括三个:clk的上跳沿、a的上跳沿、a的下跳沿。

二、疑难:

b一定要在一个always块中被赋值,所以需要在一个always块中区分clk的上跳沿、a的上跳沿和a的下跳沿

百思不得其解,特发此贴求助!

老兄,图挂了

http://s6.sinaimg.cn/middle/68fb9cba4ac2c46359a45&690

你把图传上来多好啊,回帖时采用高级模式,里面有一个图标用来上传图片

上传不了,可能是网络的原因,蛋疼了

[attach]396155[/attach]帮lz贴图

异步设计有何诀窍?

我已经帮小编在前面的回帖中贴好了,不知道你为什么也没有贴图成功?

将a用寄存器打一拍,然后和原来的a异或一下就出来了b这个信号了

verilog代码写不来,给你写个vhdl的。

process(clk)

begin

if rising_Edge(clk) then

a_p<=a;

end if;

end process;

b<=a xor x_p;

不知是不是这个意思

服了,没想到用中间信号

小编正解!

如果是verilog的话就是:

assign b = a^c;

always @(posedge clk)

c <= a;

采用中间变量,最后xor一下即可

a是完全异步的,打一拍使用是不是不可靠?

我觉得应该先把a用clk打两拍,再delay一拍,异或得出b。

这样的话,b的timing会整体后移两个周期。

小编牛拜

看不到图片 能给我发一个吗 谢谢

这个其实就是相当于上升沿检测,和下降沿检测。

有整个题目吗

就是一个常用的边缘检测电路。

题目估计有些前提条件什么的吧 比如不考虑建立时间什么的

好像看一下,它跟时钟好像不同步,貌似不行。待看下文。

这是个上升沿检测电路,10楼正解

膜拜下。看了好一会儿才看明白。

其实是要跳出思维定势,平时可能时序电路接触的比较多,就不会想到用组合电路来做

always@(clk)

a_q <= a;

assign b = a ^ a_q;

楼上的写错了,少了posedge

话说这个题目应该还是挺基础的

确实是写错了,少写了个posedge。谢谢指正

这就是个 双沿的 edge detector

可以用mealy fsm实现

moore就不行了 太慢

//This is a dual-edge detector based on mealy FSM

module detector

(

input wire clk, reset,

input wire level,

output reg tick

);

localparam zero = 1'b0,

one = 1'b1;

reg state_reg, state_next;

always @(posedge clk, posedge reset)

begin

if (reset)

state_reg <= zero;

else

state_reg <= state_next;

end

always @*

begin

state_next = state_reg;

tick = 1'b0;

case (state_reg)

zero:

begin

if (level)

begin

state_next = one;

tick = 1'b1;

end

end

one:

begin

if (!level)

begin

state_next = zero;

tick = 1'b1;

end

end

default: state_next = zero;

endcase

end

endmodule

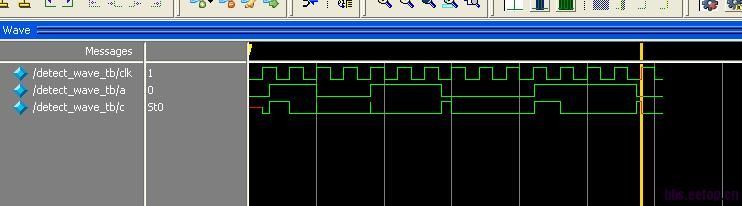

testbench波形图

代码如下:

module detect_wave(input clk,a,

output c

);

reg b;

always @(posedge clk)

begin

b=a;

end

assign c=a^b;

endmodule

`timescale 1ns/10ps

module detect_wave_tb;

reg clk,a;

// instantitate the unit under test

detect_wave uut( .clk(clk),.a(a),.c(c));

initial

begin

clk=0;

a=0;

#15;

a=1;

#35;

a=0;

#40;

a=1;

#52;

a=0;

#69;

a=1;

#75;

a=0;

#20;

$stop;

end

always #10 clk=~clk;

endmodule

a与clk是异步的,不知道大家为何都可以不同步直接用clk采样a来使用!?

小编高手,答案懂了 ,只几行而已,可是很巧妙诶。话说这个结果是怎么推算出来的呢?经验吗?猜的吗?