Block RAM问题

时间:10-02

整理:3721RD

点击:

初学ISE 测试IP core 生成了一个单口RAM, 直接把个端口接出来,读写数据,发现读出的数据一致是00

该给的时序都给了,不知道是什么原因

代码如下:

module test_ram(

input clk,

input [7:0] dina,

input [7:0] addr,

input wea,

input ssra,

output douta

);

ram ram_t(

.clka(clka),

.dina(dina),

.addra(addra),

.wea(wea),

.ssra(ssra),

.douta(douta)

);

endmodule

tb文件如下:

module tb;

// Inputs

reg clk;

reg [7:0] dina;

reg [7:0] addr;

reg wea;

reg ssra;

// Outputs

wire [7:0] douta;

// Instantiate the Unit Under Test (UUT)

test_ram uut (

.clk(clk),

.dina(dina),

.addr(addr),

.wea(wea),

.ssra(ssra),

.douta(douta)

);

initial begin

// Initialize Inputs

clk = 0;

dina = 0;

addr = 0;

wea = 1;

ssra=1;

// Wait 100 ns for global reset to finish

#100;

ssra=0;

// Add stimulus here

end

always #10 clk=~clk;

always #20 begin dina=dina+1; addr=dina; end

endmodule

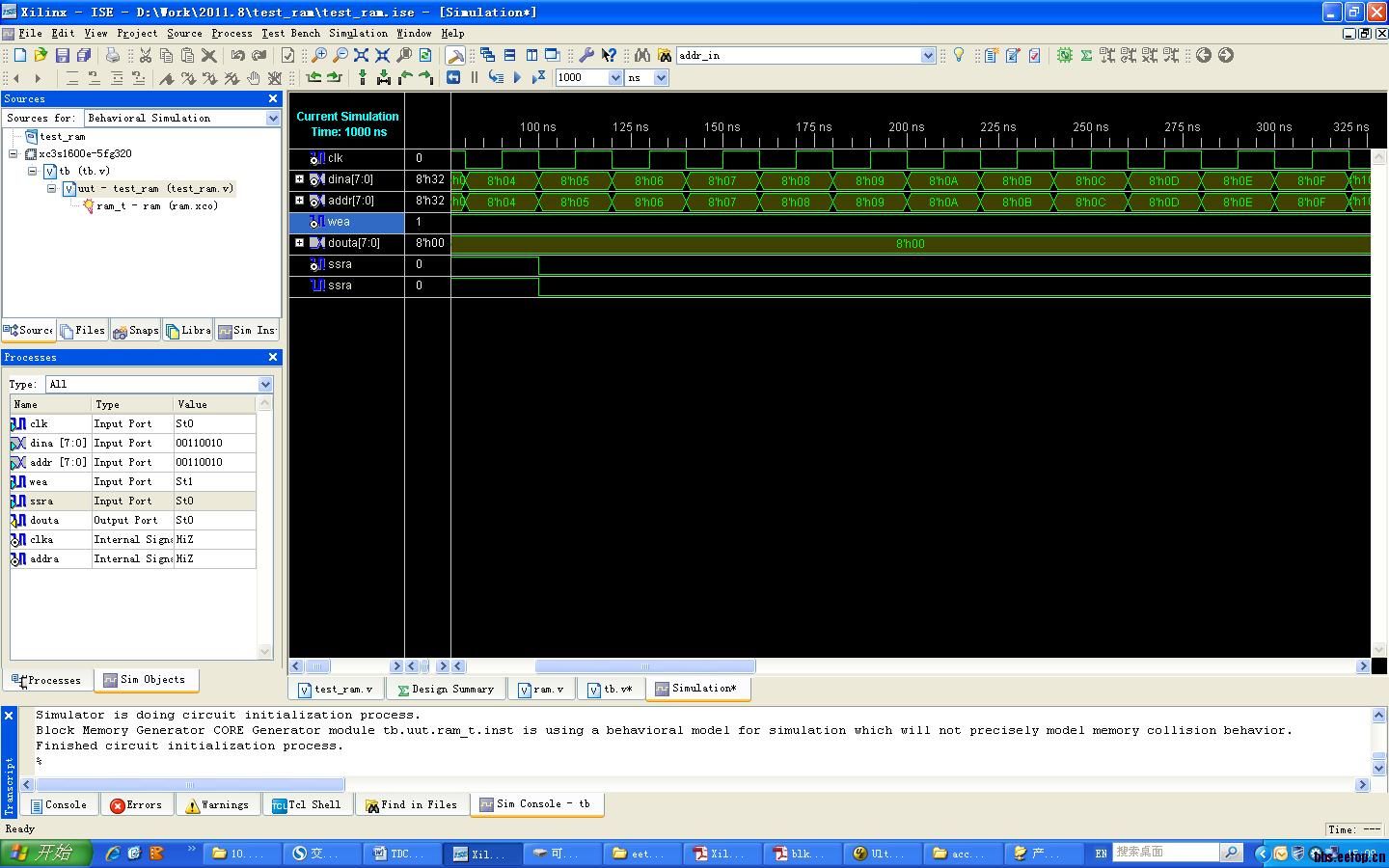

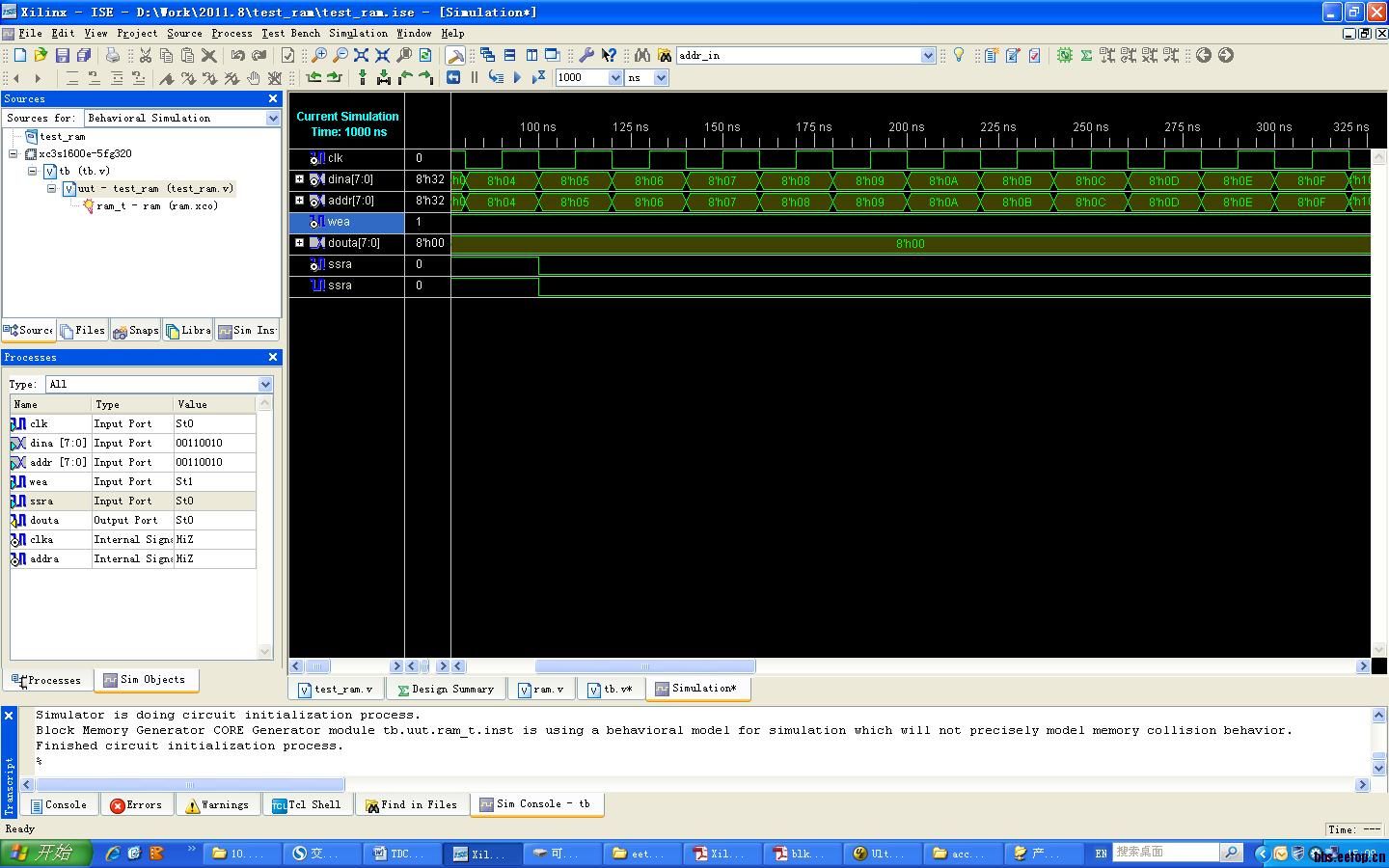

仿真图如下:

该给的时序都给了,不知道是什么原因

代码如下:

module test_ram(

input clk,

input [7:0] dina,

input [7:0] addr,

input wea,

input ssra,

output douta

);

ram ram_t(

.clka(clka),

.dina(dina),

.addra(addra),

.wea(wea),

.ssra(ssra),

.douta(douta)

);

endmodule

tb文件如下:

module tb;

// Inputs

reg clk;

reg [7:0] dina;

reg [7:0] addr;

reg wea;

reg ssra;

// Outputs

wire [7:0] douta;

// Instantiate the Unit Under Test (UUT)

test_ram uut (

.clk(clk),

.dina(dina),

.addr(addr),

.wea(wea),

.ssra(ssra),

.douta(douta)

);

initial begin

// Initialize Inputs

clk = 0;

dina = 0;

addr = 0;

wea = 1;

ssra=1;

// Wait 100 ns for global reset to finish

#100;

ssra=0;

// Add stimulus here

end

always #10 clk=~clk;

always #20 begin dina=dina+1; addr=dina; end

endmodule

仿真图如下:

在线等啊~!~

不知道是不是SSRA的问题,你试试把SSRA先1后0行不。

有没有可能是没有编译库,无法仿真?

在ISE10.1中,wea = 1是读状态;而在ISE13.1中,wea = 1是写状态的

看一下有没有弄混的啊

不是复位和wea的问题,很是奇怪,搞不懂ISE了

你什么时候写文件了?

开机一直在写,觉得再怎么错误也该出个乱码吧,时钟,时能,数据都有

只见写,不见读。

单口RAM无论读写有地址和时钟就有数据输出啊

单口RAM read、write 在同一时刻同一地址时,read 出来的值是unknown的。

恩,但就是不出数,很诧异~

你想读的地址都是未写入的地址,写入后的地址有读吗?

这段波形里面看不到。

凡事简单点,自己造个coe初始化下。我就不信读不出来了

一样的,而且我用的是write first,按理来说肯定是有数据出来的~

多放几段波形吧,写一轮以后的波形是怎样的?

这段波形只看到写,没看到读啊。

你写完了,再读一下,看看是不是写进去了。

综合的RAM也有不同种类的,有可能仿真模型输出未写入的地址数据就是0啊。![]()

1、先确定是不是SSRA的设置有问题,可以先把它从IP核中去掉,或者在testbench中把它的值反一下

2、IP核设置页面的第二页里面,有个operating mode设置项,如果是设置成No change,那么在写过程中,读端口将会保持不变的。

试一下,希望会有帮助

ok , got it!