各位老大帮帮忙了!(关于一个用verilog可编程的分频器的分析)

时间:10-02

整理:3721RD

点击:

[这个贴子最后由holypal在 2005/11/02 12:40pm 第 1 次编辑]

哪位老大帮忙分析一下下面这个可编程的分频器(4档: 8. 16. 32. 64)

源程序如下:

module clk_sync(sclk, din, reset_n, R_freq_div, clk_out);

inputsclk;

inputdin;

inputreset_n;

input [3:0]R_freq_div;

outputclk_out;

reg [5:0] R_clk_cnt;

reg [2:0] R_clk_sync;

always @(negedge sclk or negedge reset_n) begin

if (~reset_n)

R_clk_sync <= 3'b0;

else

R_clk_sync <= {din, R_clk_sync[2:1]};

end

wire clk_syn_cmd = ({din, R_clk_sync} == 4'b1100);

wire[5:0]clk_cnt = R_clk_cnt + 1;

regR_clk_src;

regclk_src;

always @(R_freq_div or R_clk_cnt) begin

if (R_freq_div[0])

clk_src = R_clk_cnt[2];

else if (R_freq_div[1])

clk_src = R_clk_cnt[3];

else if (R_freq_div[2])

clk_src = R_clk_cnt[4];

else

clk_src = R_clk_cnt[5];

end

always @(negedge sclk) begin

R_clk_cnt <= clk_syn_cmd ? {R_freq_div, 2'b0} : clk_cnt;

end

always @(negedge sclk or negedge reset_n) begin

if (~reset_n)

R_clk_src <= 0;

else

R_clk_src <= clk_src;

end

assignclk_out = R_clk_src;

endmodule // Mclk_sync

哪位老大帮忙分析一下下面这个可编程的分频器(4档: 8. 16. 32. 64)

源程序如下:

module clk_sync(sclk, din, reset_n, R_freq_div, clk_out);

inputsclk;

inputdin;

inputreset_n;

input [3:0]R_freq_div;

outputclk_out;

reg [5:0] R_clk_cnt;

reg [2:0] R_clk_sync;

always @(negedge sclk or negedge reset_n) begin

if (~reset_n)

R_clk_sync <= 3'b0;

else

R_clk_sync <= {din, R_clk_sync[2:1]};

end

wire clk_syn_cmd = ({din, R_clk_sync} == 4'b1100);

wire[5:0]clk_cnt = R_clk_cnt + 1;

regR_clk_src;

regclk_src;

always @(R_freq_div or R_clk_cnt) begin

if (R_freq_div[0])

clk_src = R_clk_cnt[2];

else if (R_freq_div[1])

clk_src = R_clk_cnt[3];

else if (R_freq_div[2])

clk_src = R_clk_cnt[4];

else

clk_src = R_clk_cnt[5];

end

always @(negedge sclk) begin

R_clk_cnt <= clk_syn_cmd ? {R_freq_div, 2'b0} : clk_cnt;

end

always @(negedge sclk or negedge reset_n) begin

if (~reset_n)

R_clk_src <= 0;

else

R_clk_src <= clk_src;

end

assignclk_out = R_clk_src;

endmodule // Mclk_sync

各位老大帮帮忙了!(关于一个用verilog可编程的分频器的分析)

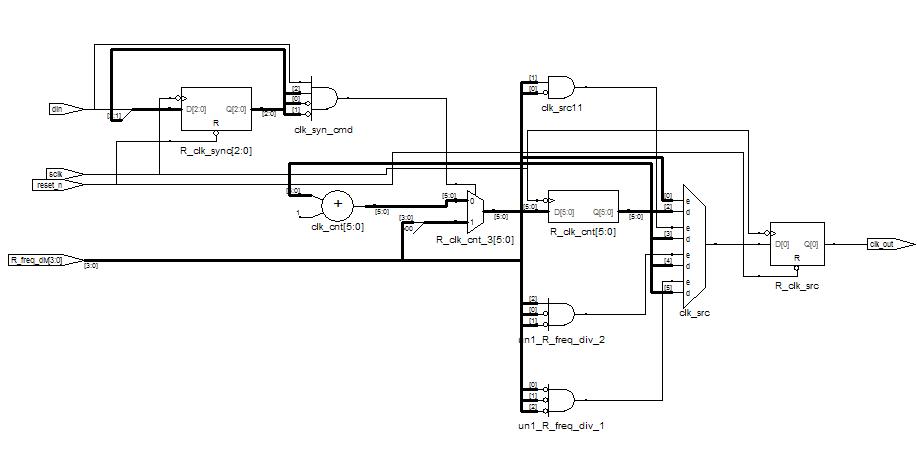

这个是综合后的RTL电路图

各位老大帮帮忙了!(关于一个用verilog可编程的分频器的分析)

在线等。。ING

KAN KAN!