求教,关于同步问题!

module Mux(

input clk_1,

input data_clk1,

input clk_2,

input data_clk2,

input clk_3,

input select_clk3,

output data_out

);

endmodule

data_clk1,在clk_1时钟域,data_clk2在clk_2时钟域,select_clk3在clk_3时钟域,该模块的功能是当select_clk3为1时,data_out输出为data_clk1(自然也为clk_1时钟域),当select_clk3为0时,data_out输出为data_clk2(自然也为clk_2时钟域)。clk_1和clk_2频率比较接近,但相位不同,clk_3的频率大致为clk_1或clk_2的2倍。

现在的问题是,怎样才能保证输出data_out不会出现毛刺,亚稳态?

新手,不太清楚要怎样做比较好,望高手指教!

do clk1,clk2,clk3 synch or asynch ?if synch, you can use register triggered by clk3 because the output of comb is glitch possible.

module MUX();

input clk1,clk2,clk3,select_clk3;

input data_clk1,data_clk2;

output data_out;

reg data_out;

reg data1,data_clk1_r, data_clk1_rr;

reg data2,data_clk2_r, data_clk2_rr;

always@(posedge[/email] clk1)

data1<=data_clk1;

always@(posedge[/email] clk2)

data2<=data_clk2;

always@(posedge[/email] clk3)

begin

data_clk1_r<=data1;

data_clk1_rr<=data_clk1_r;

end

always@(posedge[/email] clk3)

begin

data_clk2_r<=data2;

data_clk2_rr<=data_clk2_r;

end

assign data_out=(select_clk3==1'b1)?data_clk1_rr:data_clk2_rr;

endmodule

没碰到过这种问题,不懂。

我也想知道

根据你所说,选择信号频率是被选择信号的2倍左右,那么怎么可能输出完整的clk1或clk2呢?

感觉你说的不够清楚,能否把画个图,把信号之间的关系表述的清楚具体点,这样高手们也好帮到你啊?!

过来看看

个人觉得这种同步问题的关键是时钟域的切换,不同的时钟域选择相应时钟域的数据值。

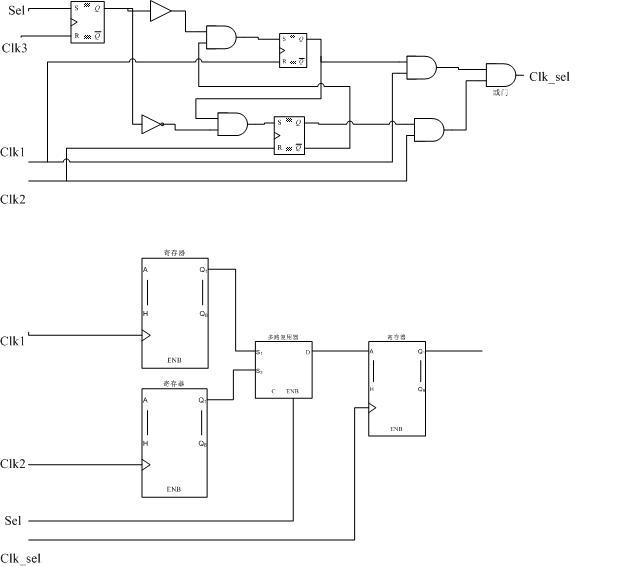

用visio画了下电路图,大家讨论下是否可行

先有电路再有代码,代码是描述电路的,并不是有代码而有电路。

XIEXIE !