RTL视图上控制二进制数范围的算法

时间:10-02

整理:3721RD

点击:

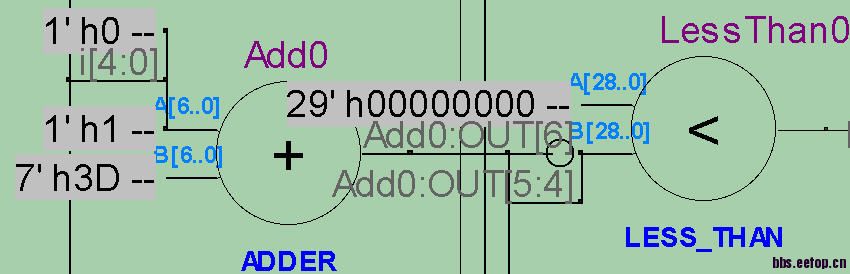

下面的代码是我根据对这个局部图的理解描述的,请问这个例子如何推广到更一般的情况?即控制一个二进制数在另一个确定的大小范围内的算法,比如5'b0_0010≤i≤5'b0_1111又该如何确定下面描述中的x?

/*

控制5位二进制数i大小范围在 5'b0_0001≤i≤5'b0_1000 之间的算法

*/

wire [4:0]i;

wire [6:0]k;

wire [6:0]n;

wire [6:0]sum;

assign k={0,i,1};//在i的首尾各拼接了一位,高位是0,低位是1

assign x=7'b011_1101;//利用这个数x和拼接之后的数k相加,不知道这个数是如何确定的

assign Sum=x+k;

always @(posedge CLK or negedge RSTn)

if(sum[6]==1 && sum[5]==0 && sum[4]==0 )//求和之后考查高三位,如果为100,那么i就满足5'b0_0001≤i≤5'b0_1000

//5'b0_0001≤i≤5'b0_1000

麻烦大侠告诉我这个算法的名字或者资料也行,我自己去搜