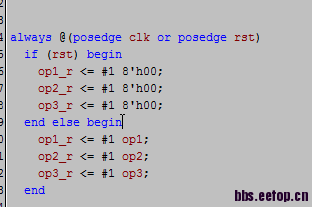

RTL代码

时间:10-02

整理:3721RD

点击:

最近在看verilog的书,书上说rtl级的代码加了延时后,在综合的时候会直接忽略,但是我看到上面这个代码都加了一个时间单位的延时,我想问一下加这个延时是不是有没有什么作用啊?

最近在看verilog的书,书上说rtl级的代码加了延时后,在综合的时候会直接忽略,但是我看到上面这个代码都加了一个时间单位的延时,我想问一下加这个延时是不是有没有什么作用啊?

这个延时只用于仿真,看波形图方便。综合的时候会忽略掉。

2楼正解,这是为了方便仿真而已

这样加为了查看波形方便,会不会有综合前后时序不一样的问题?

综合前,加延时和不加延时,会不会出现的结果不一样?

小弟请教一下

会被忽略掉,一样的

小编,能不能解释的更详细一下啊。

举一个例子讲讲啊,小弟求解啊。

我们公司coding的时候都要加延迟的。前仿的时候debug很方便,综合的时候会有个warning提示延迟被忽略。

rtl 加 delay 主要就是 方便查看波形。其实code仿真可以说是忽略timing的,即理想情况。

无所谓,加不加都一样,加了之后前仿波形中数据和时钟沿之间有延时,类似后仿波形,只是延时不一样而已

在综合前后时序肯定不一样,综合前的RTL代码是没有延时的,如果写了#1,那么在仿真的时候会有1个时间单位的延时。而综合后的延时取决于具体的工艺器件延时和线延时了。但是这些在正常情况下不会导致simulation和具体电路mismatch的情况。除了以下情形:

1. 综合时序约束错误。这种错误是综合的问题,和RTL代码是否延时1个时间单位,没关系。

2. 需要综合的时间周期小于这里约束的延时时间,比如这里#1是1纳秒,但是这个电路你要综合在1吉的速度甚至更快。那么其一个时钟周期就已经小于1纳秒了。显然这里延时1纳秒是不恰当的。

谢谢小编。小弟学习了。