三段式与两段式状态机

时间:10-02

整理:3721RD

点击:

最近对一大片时序,脑袋有点迷糊了,总是感觉有些地方和其他人的差一个clk,我看了下,我用的是三段式FSM,同学用的是两段式的,是不是三段式的输出是不是会经过一个触发器打一节拍,所以慢一个clk(有点晕),不知道这样会不会有影响?

两段式才容易出错 三段式是主流 所以你不要担心自己的代码出问题 两段式组合逻辑太长很容易时序violation

时序和写法无关。

同一个时序要求,不管用一段两段还是三段,应该都可以实现。

小编说的对。两段式,一段时状态的转移描述,用到触发器,第二段是逻辑组合电路,涉及下一状态赋值和输出。三段式里把两段式分为两段,分别是下一状态赋值和输出电路,并在输出电路上加了触发器,所以输出会慢一拍。

重在电路结构,代码只是浮云!

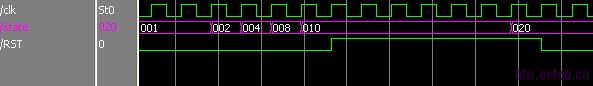

不是太清楚,以前好像是在哪里看过说三段式最后要经过一个触发器来同步化,所以相对于不用这个always语句的要多一个clk,不知道是不是这个样子的,如果不是这个引起的,就不知道波形为什么会延迟一个时钟周期了!

下面这张图也是这样

嗯!

但是我的结构要用我的代码作为载体,而且就算我慢一拍,还是可以满足我的时序上的要求!所以想要探讨一下!

慢一拍的差异就是输出多了一个触发器,是这么理解的,但实际上时序不会有什么问题。