学校的FPGA 设计---交通灯卫星控制器

分频模块:

module fenpinqi(clk,rst,clk_odd);

input

clk,rst;

output

clk_odd;

reg

clk_odd;

reg[13:0]

count;

parameter

N = 10000;

always @ (posedge clk)

if(! rst)

begin

count <= 1'b0;

clk_odd <= 1'b0;

end

else

if ( count < N/2-1)

begin

count <= count + 1'b1;

end

else

begin

count <= 1'b0;

clk_odd <= ~clk_odd;

end

endmodule

控制及计时模块:

module control(led,car,rst,clk,count_H_1,count_L_1,count_H_2,count_L_2);

output [3:0]count_H_1,count_L_1,count_H_2,count_L_2;

output [5:0]led;

input clk,rst,car;

reg [5:0] led;

reg [3:0]count_H_1,count_L_1,count_H_2,count_L_2;

reg [1:0]state;

parameter S0=2'b00,

S1=2'b01,

S2=2'b10,

S3=2'b11;

always @(posedge clk or negedge rst)

if(!rst)

begin

led=6'b010100;

state=S0;

count_H_1=4'b0000;count_L_1=4'b0000;

count_H_2=4'b0000;count_L_2=4'b0000;

end

else

begin

case(state)

S0:

begin

if(!car)

begin

led=6'b010100;

count_H_1=4'b0100;count_L_1=4'b0101;

end

else if(count_L_1==0)

begin

if(count_H_1==0)

begin

led=6'b001100;

count_H_1=4'b0000;count_L_1=4'b0100;

state<=S1;

end

else

begin

count_H_1<=count_H_1-1'b1;

count_L_1<=4'b1001;

end

end

else begin

count_L_1<=count_L_1-1'b1;

//

count_L_2<=count_L_2-1'b1;

end

if(!car)

begin

count_H_2=4'b0101;count_L_2=4'b0000;

end

else if(count_L_2==0)

begin

count_H_2<=count_H_2-1'b1;

count_L_2<=4'b1001;

end

else begin

count_L_2<=count_L_2-1'b1;

end

end

S1:

begin

if(count_L_1==0)

begin

if(count_H_1==0)

begin

led=6'b100010;

count_H_1=4'b0010;count_L_1=4'b1001;

count_H_2=4'b0010;count_L_2=4'b0100;

state<=S2;

end

else

begin

count_H_1<=count_H_1-1'b1;

count_H_2<=count_H_2-1'b1;

end

end

else begin

count_L_1<=count_L_1-1'b1;

count_L_2<=count_L_2-1'b1;

end

end

S2:

begin

if(count_L_2==0)

begin

if(count_H_2==0)

begin

led=6'b100001;

count_H_2=4'b0000;count_L_2=4'b0100;

state<=S3;

end

else

begin

count_H_2<=count_H_2-1'b1;

count_L_2=4'b1001;

end

end

else begin

count_L_2<=count_L_2-1'b1;

end

if(count_L_1==0)

begin

begin

count_H_1<=count_H_1-1'b1;

count_L_1=4'b1001;

end

end

else begin

count_L_1<=count_L_1-1'b1;

end

end

S3:

begin

if(count_L_2==0)

begin

if(count_H_2==0)

begin

led=6'b010100;

count_H_1=4'b0100;count_L_1=4'b1001;

count_H_2=4'b0100;count_L_2=4'b0100;

state<=S0;

end

else

begin

count_H_1<=count_H_1-1'b1;

count_H_2<=count_H_2-1'b1;

end

end

else

begin

count_L_1<=count_L_1-1'b1;

count_L_2<=count_L_2-1'b1;

end

end

endcase

end

endmodule

扫描译码显示模块:

module saomiao(rst,clk,count_H_1,count_L_1,count_H_2,count_L_2,sel,seg);

input rst,clk;

input [3:0]count_H_1,count_L_1,count_H_2,count_L_2;

output [6:0]sel;

output [3:0]seg;

reg [6:0]sel;

reg [3:0]seg;

reg [15:0] count;

reg [1:0] cnt;

reg

[3:0] data;

reg clk_odd;

always@(posedge clk or negedge rst)//50M-1k,50M/1k/2//?,50Mhz~1khz,?50%

begin

if(!rst)begin

count<=0;

clk_odd<=0;

end

else if(count==16'd2)

begin

clk_odd<=~clk_odd;

count<=0;

end

else

count<=count+1'b1;

end

always @(negedge rst or posedge clk_odd)//?1ms

if (!rst)begin

cnt<=2'b00;

end

else cnt<=cnt+1'b1;

always@(negedge rst or posedge clk)

//?

if(!rst)

begin

// sel = 7'b0000000 ;

seg = 4'b1111 ;

end

else begin

case (cnt)

2'b00: begin

seg =4'b1110 ;// ?

data=count_H_1;

end

2'b01: begin

seg

= 4'b1101 ;// ?

data

=count_L_1;

end

2'b10:begin // ?

seg= 4'b1011 ;

data=count_H_2;

end

2'b11: begin// ?

seg= 4'b0111 ;

data=count_L_2;

end

default :

begin

//

sel = 8'b0000000 ;

seg = 4'b0000 ;

end

endcase

end

always @ (data or seg)begin

case(data)

4'b0000:sel=7'b1111110;

4'b0001:sel=7'b0110000;

4'b0010:sel=7'b1101101;

4'b0011:sel=7'b1111001;

4'b0100:sel=7'b0110011;

4'b0101:sel=7'b1011011;

4'b0110:sel=7'b1011111;

4'b0111:sel=7'b1110000;

4'b1000:sel=7'b1111111;

4'b1001:sel=7'b1111011;

default:sel=7'b1111110;

endcase

end

endmodule

顶层模块:

module jiaotongdeng(clk,rst,car,led,sel,seg);

input clk,rst,car;

output [3:0] seg;

output [6:0] sel;

output [5:0] led;

wire [3:0]count_H_1,count_L_1,count_H_2,count_L_2;

wire

clk_odd;

saomiao ee(rst,clk,count_H_1,count_L_1,count_H_2,count_L_2,sel,seg);

control rr(led,car,rst,clk_odd,count_H_1,count_L_1,count_H_2,count_L_2);

fenpinqi tt(clk,rst,clk_odd);

endmodule

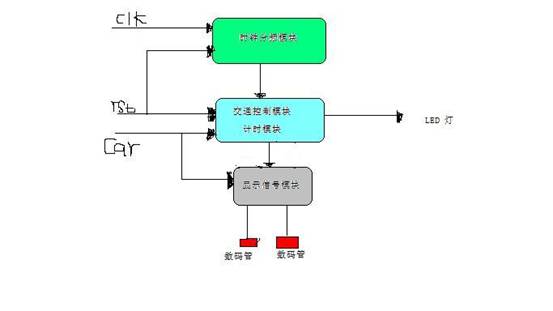

它的设计图

有勇气不学就要有勇气宕。

呵呵 今天早上 仔细看了一下 里面有些错误 已经改了...

学习下

学习下

同样是新手