模块实例化遇到点问题,在线等大牛帮助

时间:10-02

整理:3721RD

点击:

- `timescale 1ns / 1ps

- `include "D:/Verilog_work/add/Adder_21bits.v"

- module add(

- //input

- ina,inb,inc,

- //output

- oc,result,choosea,chooseb

- );

- input [20:0] ina,inb;

- input inc ;

- output oc;

- output [20:0] result,choosea,chooseb;

- reg [20:0] result;

- reg in_cin = 0 ;

- reg [20:0]choosea,chooseb;

- wire[20:0]chooseresult;

- Adder_21bits add1(.in_a_21bits(choosea),.in_b_21bits(chooseb),

- .sum_21bits(chooseresult),.cin(in_cin),.cout(oc));

- always @(ina,inb,inc)

- begin

- if(ina[20] ==0)

- begin

- choosea = ina;

- end

- else

- begin

- choosea = {ina[20],~ina[19:0]+1};

- end

- if(inb[20] ==0)

- begin

- chooseb = inb;

- end

- else

- begin

- chooseb = {inb[20],~inb[19:0]+1};

- end

- if(chooseresult[20] ==0)

- begin

- result = chooseresult;

- end

- else

- begin

- result = {chooseresult[20],~chooseresult[19:0]+1};

- end

- end

- endmodule

为啥我直接给choosea,chooseb 赋值的时候可以得到正确的结果,这么写就不能了,加法器是正确的已经验证过

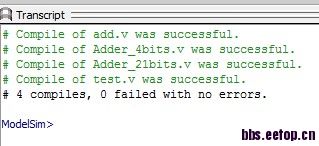

把编译的log 发上来。

另外 duv 和 testbench 激励 最好不要放在一个文件里面

那个log在哪儿看,我用的是modelsim

有个窗口, 不点变化的那个。

是这个吗

确认算法有问题不 三个都需要在复数时候取反加一么

没有看懂

chooseresult

这个信号要添加到这个always块的敏感电平列表中。