帮忙看一下为什么没有输出?

时间:10-02

整理:3721RD

点击:

module rd_logic(

clk,

rst,

wr_ack,

valid,

rd_en

);

input clk;

input rst;

input wr_ack;

input valid;

output rd_en;

reg [5:0] wr_count=6'b000000;

reg [5:0] temp=6'b000000;

reg rd_en;

always @(posedge clk or posedge rst)

begin

if(rst)

wr_count<=0;

else

begin

if((wr_ack==1)&&(valid==0))

wr_count<=wr_count+6'b000001;

else

begin

if(wr_count==6'b110010)

begin

temp<=wr_count;

wr_count<=0;

if((wr_ack==0)&&(valid==1))

temp<=temp-6'b000001;

else

temp<=temp;

end

else

wr_count<=wr_count;

end

end

end

always @(posedge clk or posedge rst)

begin

if(rst)

rd_en<=0;

else

begin

if(temp==6'b110010)

rd_en<=1;

else if (temp==6'b000000)

rd_en<=0;

else

rd_en<=rd_en;

end

end

endmodule

说明:利用wr_count 计数,为50时,rd_en有效,开始读数据,将wr_count的值赋给一个临时变量temp,成功读出一个数据时,temp值减1,直到temp值为零时,表示着五十个数据已经成功读出,再进行计数,满五十重复以上操作。

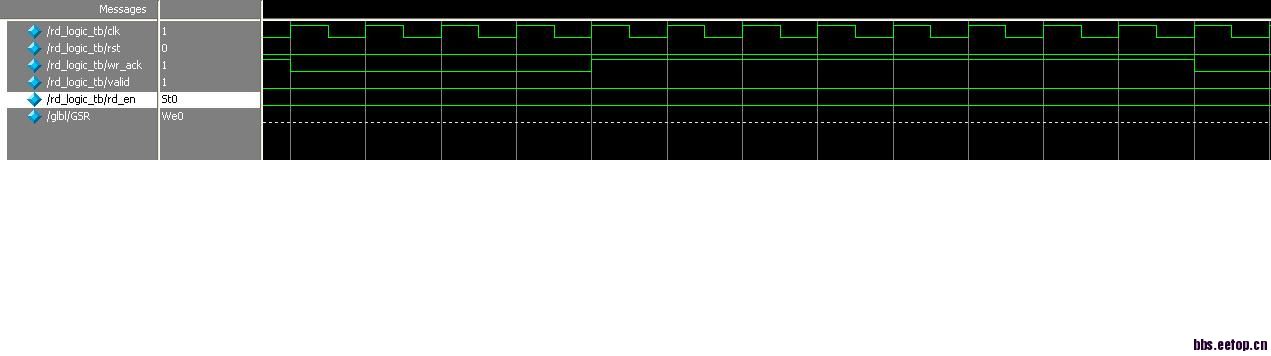

可是输出一直为零,不知道哪里的逻辑不对,帮忙看看,谢谢!

clk,

rst,

wr_ack,

valid,

rd_en

);

input clk;

input rst;

input wr_ack;

input valid;

output rd_en;

reg [5:0] wr_count=6'b000000;

reg [5:0] temp=6'b000000;

reg rd_en;

always @(posedge clk or posedge rst)

begin

if(rst)

wr_count<=0;

else

begin

if((wr_ack==1)&&(valid==0))

wr_count<=wr_count+6'b000001;

else

begin

if(wr_count==6'b110010)

begin

temp<=wr_count;

wr_count<=0;

if((wr_ack==0)&&(valid==1))

temp<=temp-6'b000001;

else

temp<=temp;

end

else

wr_count<=wr_count;

end

end

end

always @(posedge clk or posedge rst)

begin

if(rst)

rd_en<=0;

else

begin

if(temp==6'b110010)

rd_en<=1;

else if (temp==6'b000000)

rd_en<=0;

else

rd_en<=rd_en;

end

end

endmodule

说明:利用wr_count 计数,为50时,rd_en有效,开始读数据,将wr_count的值赋给一个临时变量temp,成功读出一个数据时,temp值减1,直到temp值为零时,表示着五十个数据已经成功读出,再进行计数,满五十重复以上操作。

可是输出一直为零,不知道哪里的逻辑不对,帮忙看看,谢谢!

什么狗屁code

首先,你的reg [5:0] wr_count=6'b000000; reg [5:0] temp=6'b000000;这么写是不对的,仿真没有问题,综合的时候会出错的,应该在复位模块中对其赋值。

其次,我觉得问题可能出在temp<=wr_count; wr_count<=0;你好好想想你的时序。

首先,你的reg [5:0] wr_count=6'b000000; reg [5:0] temp=6'b000000;这么写是不对的,仿真没有问题,综合的时候会出错的,应该在复位模块中对其赋值。

其次,我觉得问题可能出在temp<=wr_count; wr_count<=0;你好好想想你的时序。

哪凉快哪呆着去,得瑟什么呀!

嗯,好,我在仔细检查一下~

说实话写的确实很不怎么样。reg [5:0] wr_count=6'b000000 意思是wr_count是恒定值。如果你想赋初始值,在testbanch里用initial语句。你写的是 if((wr_ack==1)&&(valid==0))时计数器加1,加到50时有输出,可你波形图里wr_ack==1&&valid==0才有几个周期啊?还有好多逻辑错误,看着感觉像第一次写代码似的

仿真看一下temp的值是否正确

问题有可能是出在这里的

然后再确认一下testbench有没有问题的

刚学不久