关于quartus的时序仿真问题!

时间:10-02

整理:3721RD

点击:

声明本人菜鸟一个!

今天遇到个问题,主要是在此之前也没在意!

如下很简单的一段代码。降频、分频的用的,想实现8分之1的CLK的频率。

然后时序仿真,第一次用,有点跛脚!

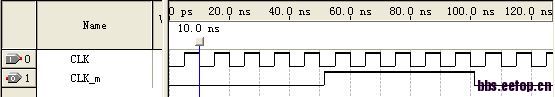

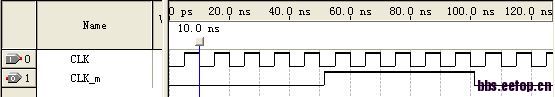

仿真的时序图我感觉不对!

我明明写的CLK_m是在CLK的第四个上升沿翻转(~CLK_m),可是仿真图却是在第五个下降沿之后翻转。

我试过很多次,调整了参数,反正都是在都是在n+1的下降沿之后翻转。这软件是不是有问题。还是我想的不对!

今天遇到个问题,主要是在此之前也没在意!

如下很简单的一段代码。降频、分频的用的,想实现8分之1的CLK的频率。

然后时序仿真,第一次用,有点跛脚!

- module test(CLK,CLK_m);

- input CLK;

- output reg CLK_m;

- reg [4:0] count;

- always@(posedge CLK)

- if(count==5'd4)

- begin

- CLK_m<=~CLK_m;

- count<=0;

- end

- else

- count<=count+1;

- endmodule

仿真的时序图我感觉不对!

我明明写的CLK_m是在CLK的第四个上升沿翻转(~CLK_m),可是仿真图却是在第五个下降沿之后翻转。

我试过很多次,调整了参数,反正都是在都是在n+1的下降沿之后翻转。这软件是不是有问题。还是我想的不对!

自己的贴顶起1

看你综合出来的电路,而且这是阻塞赋值

时序仿真里面的延时是正常的,这才几个ns而已,实际中是不可能正好在你要的边沿翻转的。

0~4,计数值是5个,延迟确实有点大