NC-Verilog后仿所遇到的问题

各位大侠:

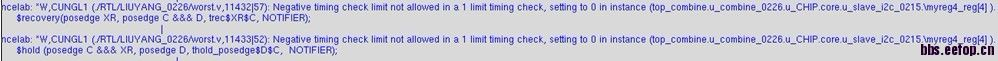

最近在用NC-Verilog 做后仿时,发现了一些问题:ncelab top -access时,它报了大量的warning,大致是一个原因的warning:

图片没有传好,几个关键字是:Negative timing check limit not allowed in a 1 limit timing check, setting to 0 in instance.

开始上网查了资料,说是负延迟,按所说方法(-neg_tchk或者是-noneg_tchk)均没有用。

请问它的warning是不是说:NC-Verilog将负延迟变为0 了?该怎么解决呢?

请各位高人指教!不甚感激!

还是贴个图吧~

一般来讲,仿真工具在默认情况下,是会将负值当成0处理,这样一来,约束就会更紧

如果想正常处理这些负延迟数值,除了要添加仿真工具使能选项之外,还要确认SDF文件或者specify模型中,关于时序定义是否支持负值,比如$setup不支持,而$setuphold就支持

谢谢您的回复。对于这句话:“还要确认SDF文件或者specify模型中,关于时序定义是否支持负值,比如$setup不支持,而$setuphold就支持”我不是很理解,请问这个模型是我做后仿所用到的chip.sdf文件吗?请问如果不支持负值,那该怎么解决负延迟的检查呢?

您说,仿真工具在默认的情况下,会把负值当做0来处理,使得约束更紧了,是否可以这样认为,负值被当做0了,功能仍旧实现,说明未有关于负延迟的时序违例。

非常感谢!

您好!下午我看到了您以前的帖子,对您的说法有一定的了解了。现在我已经把hold全部用setuphold来代替,所以hold中没有出现负值,(setuphold中是有负值的),但是modelsim(或者NC-Verilog)仍旧不识别+neg_tchk,仍旧报错(或者warning)。还请您指点指点。

谢谢!

是与仿真模块相对应的sdf文件

也可以这么认为,对于负值,仿真工具会建立模型对相关延时数据作相应处理后,再check timing

+neg_tchk这个激活负值的选项,是vcs工具的,关于modelsim(或者NC-Verilog)请研究help文档

关于nc verilog工具,我猜想它在默认的情况下,是检查负值的($setuphold and $recrem)

我刚研究了该工具的help文档,找到如下一个选项:

ncelab -NONEG_TCHK

该选项的作用是禁止负值检查

谢谢您。查看了相关的help,NC-Verilog和modelsim都是支持+neg_tchk的。

但是加了此选项后,仍旧报错(modelsim)或报warning(NC)。不知道除了把hold改成setuphold外,还有什么可能导致其如此的原因吗?

谢谢!