状态机是应该按子模块分开设计还是总体设计?

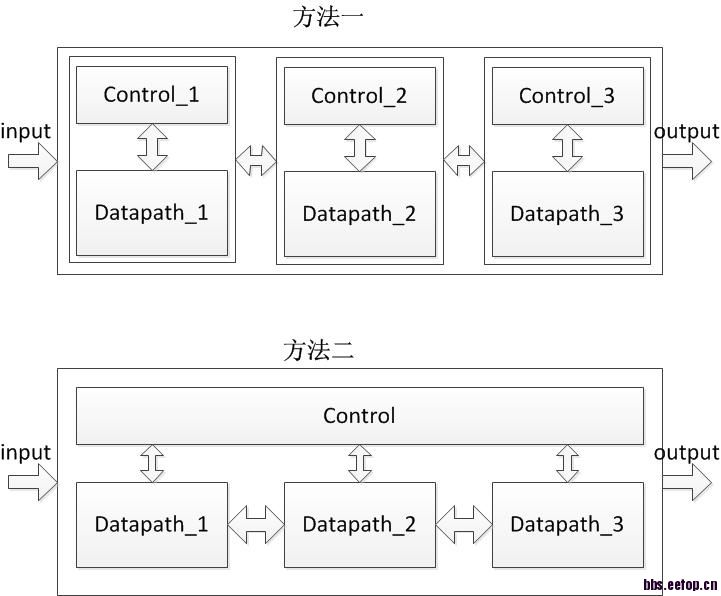

最近做一个FPGA设计,该模块由3个子模块组成,目前是把项目人员分成3部分,每部分做一个子模块,每个子模块中都有单独的状态机和数据通路,已经做完。但回想整个设计过程,我又想到了另一种设计方法,即整个顶层模块设计一个整体状态机,控制全部3个数据通路。

这2种设计思路应该各有优缺点

方法一人员分工明确,但子模块之间控制信号协议的交互比较麻烦,两两模块之间都需要有这种交互

方法二对子模块的交互信号的设计就简单得多,但整体状态机可能比较难调,而且这种大状态机可能状态数目比较多,因此可能会影响综合出来的时钟频率,如何写出状态数很多的快速FSM是一个难题。另外,在仿真过程中可能也会出现问题:各个子模块只能拿Datapath部分单独仿真,要把控制模块加上的话就只能顶层模块一起仿真了,这个工作量可能会突然变得很大。

请教有经验的高手们,你们一般是按照哪种方法做的?

个人觉得分开设计比较好,接口难可以通过规范化来解决,但是耦合的太紧难调这个问题很棘手。当然这也要看具体的需求。楼下高手继续发表意见。

恩,内部模块之间的接口规范化太重要了,我们都是FPGA新手,设计过程中没有注意到这个问题,等到大家都把各自的子模块设计完成了之后,才发现了许多问题。因此我才想到能不能用方法二来做,这样的话接口规范化就没那么难了。

肯定要分开设计,顶层模块只做例化不做逻辑。如果子模块相互的耦合严重,那时划分的问题。各个子模块一定要在功能上独立,这样维护简单,逻辑清楚,调试也容易得多

顶层模块做粘合逻辑,其他只能存在模块例化逻辑。模块划分要求接口清晰,模块间耦合度最小化,RAM使用分配均匀

分开设计是最好的,我以前也做一个比较大的状态机,弄的太复杂了,很不好调试...

设计之前要把各子模块划分好...这个很重要啊

谢谢各位大虾的高见哈!看来还是采用方法1表较好

分开设计各自加班,

合并设计一起加班。

^_^

哈哈~最经典的回答~顶!

建议在三个子状态机上加一个总状态机。

哈哈 说的 太对了 ~

状态机上再叠一个总状态机?从来没这么做过,总状态机只控制下面的3个状态机而不控制datapath?

几个子状态机之间的通信是一个问题,可能最多的调试就出在这个地方,我个人建议加一个简单的总状态机,让它来控制个个状态机的工作,最大的好处是调试的时候比较清晰明了。

当然,假如状态机之间本来就不需要通信或者协议很简单,那么这个总状态机是不需要的,但是从你的描述看我觉得加一个总状态机会有好处,而且这个状态机可以很简单,分支很少,仅仅是为了方便调试。

哦,恍然大悟!你说的加总状态机的想法其实就是提取了顶楼中2种方法的优点:

1.分开设计模块耦合度最小化的优点(即帖子中的方法一);

2.合并设计状态机调试简单的优点(即帖子中的方法二)。

二者优点合二为一,恩,看到的最好的方法!

有个问题要注意,这儿总状态机一定要简单,不要来回跳,否则你们还是得一起加班

恩,谢谢提醒,一提到加班,大家都不爽呀~

不客气

小编这个本不应该成为问题的,主要要是顶层结构设计的人有问题。

如果三个子状态机所实现的功能不是很复杂那么应该交给一个人来实现,顶层的人员只有控制input output的接口,系统频率就ok,其它应该由实现的人自己去负责。

如果三个子模块实现很复杂的功能,超过了一个人的工作量,那么三个子模块之间应该采用ram/FIFO/总线来实现连接,顶层人员也是只控制模块之间的数据结构,频率/面积要求就行了。

小编的方法一应该采用标准接口,方法二就应该安排一个人完成。

恩,我这个问题就是对目前一个刚刚完成的设计的思考。在设计初期都没考虑到复杂性的问题就直接采用了方法一,后来才想到可以用方法二。因此才有了这个帖子~