altera的lpm_mult的使用问题

时间:10-02

整理:3721RD

点击:

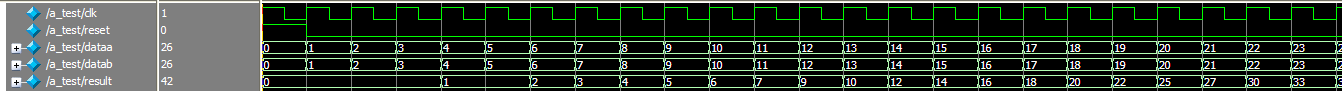

我是个初学者,请大家看看这个问题。我在项目中添加lpm_mult模块后,有lpm_mult.v、lpm_mult_bb.v和lpm_mult_sys.v三个verilog文件,仿真的时候是用_sys的文件吧。在用modelsim仿真时发现不会出现结果,仿真波形如下图:

感觉这个模块应该比较简单,但是找不到是哪里出的问题。dataa为10位,datab为6位,result为12位。

还有就是如果不采用流水线,是不是可以保证一个周期内出结果。

自己顶下,请各位牛人过来看看,谢谢了!

请各位路过的说下看法

截位的问题吧

最好把IP配置界面发过来看下

不采用流水线是可以一个周期出结果的

你这个应该是截位问题

谢谢各位。

回复 4# huizi0711

配置如下:

是不是哪里配置有问题呢?

开始的数据都没有超出范围,为什么还不对呢?

明显截位的问题啊

你可以做个测试

把输出设为16bit

你在看下结果应该是对的

还有要注意是不是无符号数相乘,这个要注意,我看你配置的是无符号数相乘

你设置的12bit输出

其实是已经截掉了16bit的低4bit

而你的输入很小

当然被截掉了

它截取的是后几位啊,我还以为是前几位呢。谢谢各位,我再试试。