关于 伪随机序列发生器,有几个问题请教下

各位好,最近在看伪随机序列发生器,看了些资料,但是有个地方还是没有看明白。

主要是从生成多项式与生成框图和verilog代码怎么对应的。

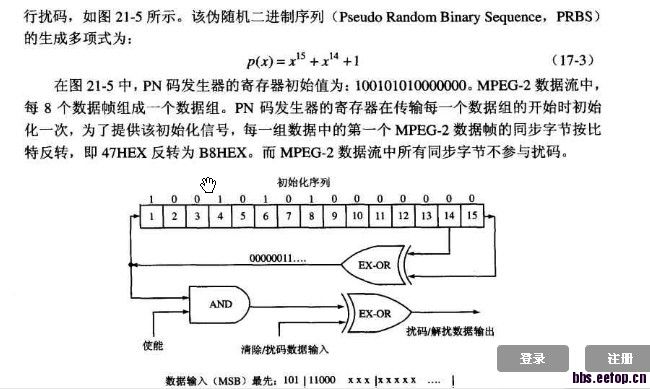

比如下面的资料:

他的生成多项式是P=X15+X14+1,但是看生成框图,只是把第14位和第15位抽头异或了,这样不就成了P=X15+X14

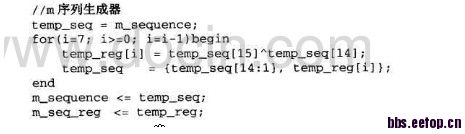

那么把“1”呢,代码里也是这样子的:

我不太明白,为什么生成多项式里的“1”在框图和程序中都不见了

还请各位熟悉的能指点一下,多谢各位了

p(x) = 0

即x14+X15=1

即D(14)+D(15) = D(0)

不好意思

本人愚钝的很,我没明白您的意思

p(x) = 0 是怎么来的?

简单的讲1就是x0,也就是input,你看最后不是还有个xor gate把输入和14,15xor的结果再xor在一起么?

那个是扰码了,另外一部分了

和伪随机序列的产生无关了

我原来也以为最低位代表1,即x的0次方,但是这样的话你发现最高位就是x的13次方和 x的14次方了,

而不是x的14次方和 x的15次方了,所以我以为应该是出于什么原因把1省略了

有没有人熟悉的,帮忙看下吧

怎么实现这个伪随机数发生器,看框图即可。

如果要搞清楚生成多项式的含义,那是一个数学问题。你得搞清楚生成多项式的数学表达的含义,除了1,另外的x^14和x^15为什么是这个写估计你也不知道。

当然我也不清楚生成多项式,只是建议你先从生成多项式的数学定义角度来分析这个问题。

感谢回答

生成多项式 这块我看了,x15+x14+1是一个本原多项式,本原多项式的求法 我也看了

我现在就是不知道在fpga实现的时候为什么不要那个1了

P=X15+X14+1

我觉得这只是一个生成多项式,而你需要是反馈系数,

从P=X15+X14+1可以看出,反馈系数c0=1, c1~c13=0, c14=1, c15=1,而c0和c15分别位于整个DFF序列的最两端,==1表示连接,==0表示断开,因为你这个是循环序列,所以一定是连接的,那么只剩下一个c14了,这样c14 ^ c15串到DFF1的输入端即可。

你这个序列的长度是15位的而不是14位的,DFF编号是从DFF1~DFF15,而不是从DFF0~DFF15

实际中多项式的最高项和最低项永远都是1

那我觉得如果这样的话应该是16位的呀,C0~C15

数字域的运算相当于Z域的运算

你把生成多项式的x换成z,每个DFF相当于乘以z exp -1(延时),这样就可以理解电路的实现了。

个人理解。