为什么block memory跑400M的时钟就出不来数据呢

时间:10-02

整理:3721RD

点击:

大家好:

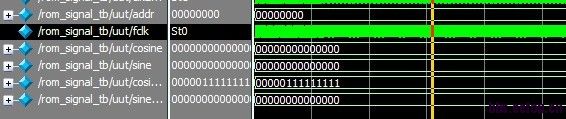

我用的是v5的xc5vlx50t的FPGA,在程序内例化了一个单端口的rom用来存波形数据的,其中rom的clk给的是400M,前仿真的时候还能有波形,但是后仿真的时候就没有波形了成为常数了,把频率降到200M后仿真后又有波形了,这是怎么回事呢?还是modelsim没有设置好呢?

时钟太高了吧,50t跑不到那么高频率

400MHz?你做下静态时序分析呢?看看是否能满足时序

时钟频率太高了,该芯片内部RAM不支持这么高的频率!

可是datasheet并没有说不能达到这么高的频率呢?为什么前仿是可以的呢

小编你确定你理解了什么是功能仿真和后仿?

先做timing analyze看看极限跑到多少,然后浮动5%一般才是你能跑频率

前仿真是理想模型,没时序信息当然没问题,你跑到几百Ghz都没问题。

小编先补充一下基本知识吧!弄清楚前仿和后仿的区别吧!

我记得V5系列的bram最高可以支持到500还是550M Hz的啊?

恩,我现在知道前仿真是没有时序的只要功能正确就能跑出来,验证功能正确与否,但是我现在还是不是很明白为什么400M的不出来波形,是不是直接就是我的时序不对了,要做时序约束了,是嘛?

对的最高可以跑到450M的,我刚仔细看了下block ram的手册

单个拿出来ROM跑跑,看看后面TIMING能不能达到!

是的!

V5的Block RAM要想跑到500Mhz,必须加上输出端口加扩展的寄存器,输出数据延时是两个时钟周期。

V5的Block RAM要想跑到500Mhz,必须加上输出端口加扩展的寄存器,输出数据延时是两个时钟周期。

学习了。

设好时序约束,看ISE跑出来的时序报告不就知道了吗

你的400m时钟是通过dcm出来的吗?我以前碰到过dcm出来的时钟在300m左右就不行,不一定是block ram模块本身不支持400m存取。