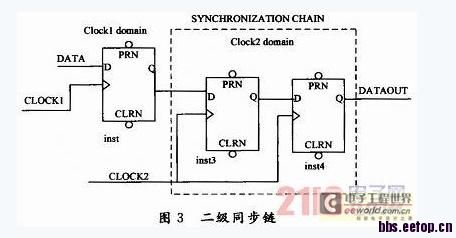

请教这个结构的作用

大家好,请教这个同步链的作用?

据说是跨时钟域的数据传输,但是怎么都看不出来

有人帮我分析一下么? 非常感谢

标准的跨时钟处理

打2拍的做法

这结构切换时钟域的,当clock1出来的信号如果通过clock2采集,可能信号正好在clock2时钟沿发生变化,这样就出现亚稳态;而通过双触发器结构,尽管第一个触发器出现亚稳态,而第二个触发器出现亚稳态的几率微乎其微,基本可消除影响。

而这种结构适用于控制信号的时钟域切换,如果需要进行数据的时钟域切换,可采用握手协议或FIFO等方法

这结构切换时钟域的,当clock1出来的信号如果通过clock2采集,可能信号正好在clock2时钟沿发生变化,这样就出现亚稳态;而通过双触发器结构,尽管第一个触发器出现亚稳态,而第二个触发器出现亚稳态的几率微乎其微,基本可消除影响。

哈哈,我等的就是这段话,“当clock1出来的信号如果通过clock2采集,可能信号正好在clock2时钟沿发生变化”,这个可能的概率太小了吧

加入一个信号只要采集一次,这个双触发器结构根本不产生任何作用嘛。信号丢失了吧

就像3楼回复的那样,我觉得,这必须保证两个时钟的上升沿高度统一啊,这个对异步时钟来说,有点牵强啊,

2个时钟不需要有关系

clock2的第一个D触发器采数据时,可能出现亚稳态。即setup 或 hold不满足,输出状态不问题,不是1 0.可能是什么中间态什么的,为了防止这个不稳定态的向下传播。影响下级电路。

于是第二个D触发器来了。这个时候再出现亚稳态的几率就会微乎其微了

这个“当clock1出来的信号如果通过clock2采集,可能信号正好在clock2时钟沿发生变化”真正含义是,信号必须满足setup和hold时间,就是说clock1出来的信号必须在clock2时钟沿前后一段时间内都是稳定的,这个概率应该大了些吧!

这种跨时钟域在实际中必然会出现亚稳态,因此LZ还是按这种经典结构处理吧

clock2的第一个D触发器采数据时,可能出现亚稳态。即setup 或 hold不满足,输出状态不问题,不是1 0.可能是什么中间态什么的,为了防止这个不稳定态的向下传播。影响下级电路。

于是第二个D触发器来了。这个时候再出现亚稳态的几率就会微乎其微了

我的问题就在这里,跨时钟数据传输,clock2的时钟下 D触发器怎么那么巧可以采集到数据?clock1和clock2之间应该有点关系吧?

如果采集到了数据,那么后面的消除亚稳态很正常,我也清楚这个方程式,

[attach]419005[/attach]

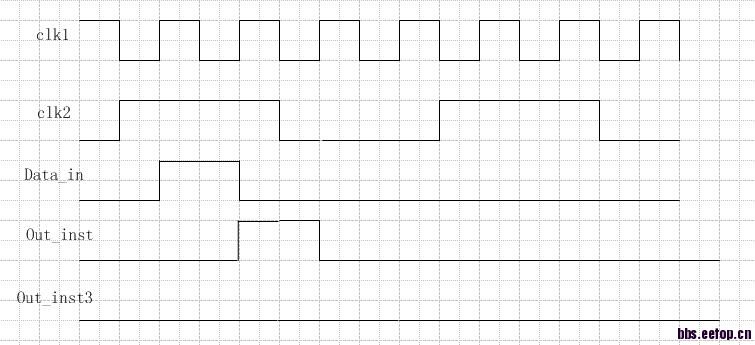

看这个图 网上现搜的

你好,我不知道这个结构的应用是不是要有什么条件?比如clk1和clk2之间的关系,下面的情况明显不合适的啊

你好,这个图怎么看啊?我看不到。

看到你的图了,呵呵我想说,这个clk1和clk2之间有一定的关系吧,比如相差不能太多

我上传的时序图,clk2频率太低,就采集不到数据的啊?

数据宽度小于时钟宽度,

当然采数会掉数了

哈哈,我晕死了,我着想了,谢谢啊,悲剧啊,非常感谢

请问,信号data_in的传输是由周期最小的时钟CLK1控制的,那么这种情况下,CLK2也相应的要等于CLK1啦?

还是说data_in的数据必须要持续几个时钟周期,必须大于CLK2?

data_in的数据持续时间,必须大于CLK2?

是有条件的,clk2时钟应该快于clk1,一般信号的脉冲宽度尽量大于2个接收时钟周期

请问楼上你用什么软件画图?

你是说时序图?visio啊

这个电路只能解决亚稳态的问题,也就是说如果从CLK1 DFF出来的数据会连接到CLK2 DFF1和CLK2 DFF2,由于在CLK2采到的是亚稳态,那么CLK2 DFF1有可能认为采到的数据是0,而CLK2 DFF2认为采到的数据是1,这样电路功能就是错了。

至于如何采到想到的数据,就是同步设计的另一个问题了,你可以使用握手,异步FIFO或者是其它某一协议来保证这个事情。

这是一个标准的同步器.但这样的同步器有他的适用范围...不是所有的跨时钟域问题都能用这样的方法解决,要具体问题,具体分析...比如像你10楼的插图.就不适合..需要先把clk1 domain的信号拉长到大过clk2的周期才行..

总之还是要看clk1,clk2的具体样子,还是clk1 domain的信号情况才能定用什么样的同步方法.