Signal Tap看到的ADC过来的数据不对?

时间:10-02

整理:3721RD

点击:

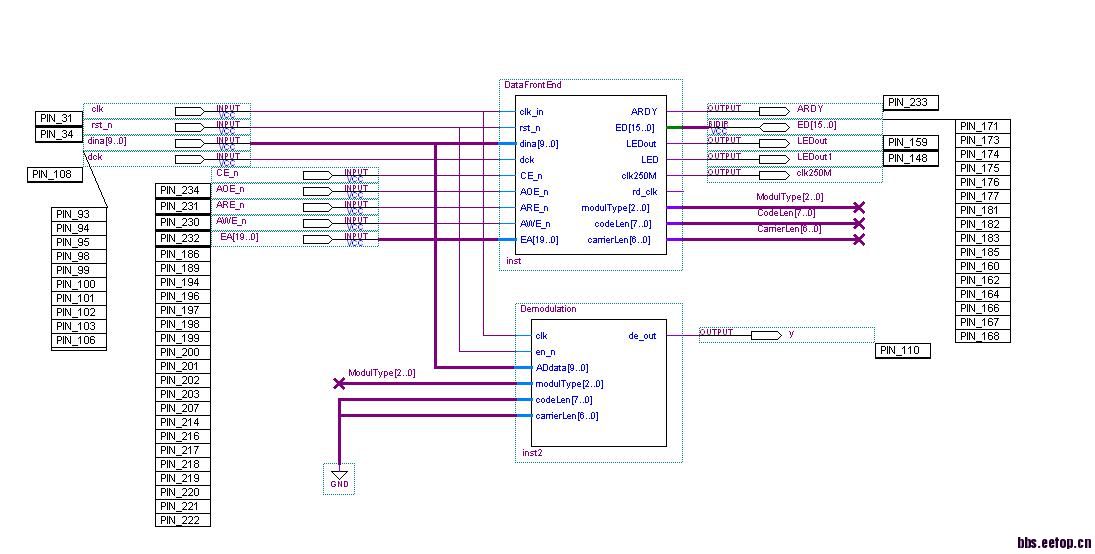

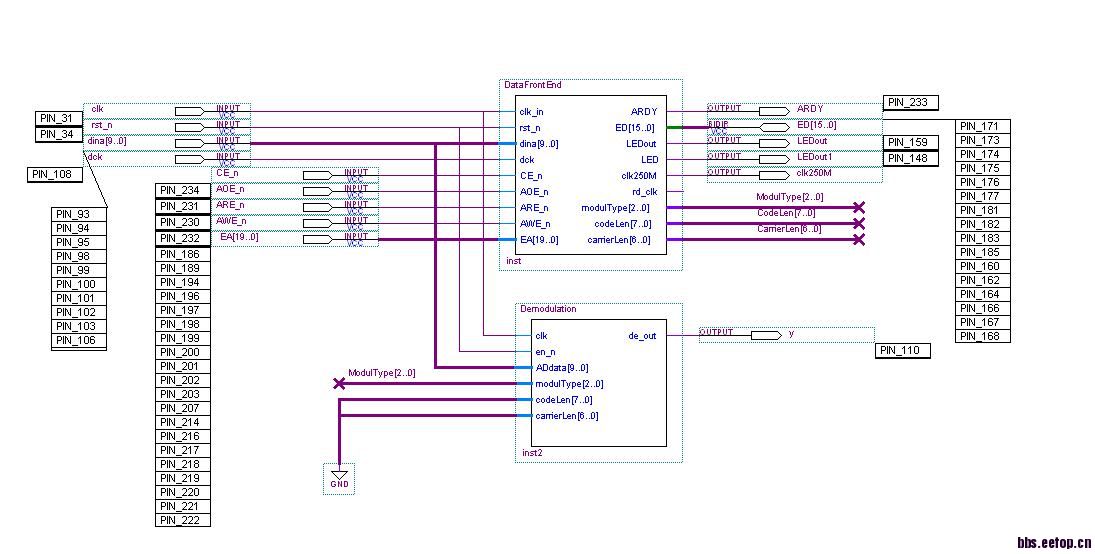

Signal Tap用250M的采样时钟,去看ADC输入的10M信号(AD采样率为100M),数据频率紊乱,严重失真。

我观测的是输入引脚进来的AD数据(dina),会不会是内部逻辑太紊乱导致输入的数据出错啊?

希望高手解答,谢谢。

[attach]406439[/attach]

我观测的是输入引脚进来的AD数据(dina),会不会是内部逻辑太紊乱导致输入的数据出错啊?

希望高手解答,谢谢。

[attach]406439[/attach]

AD过来的数据是不是本身就是存在问题的呢,可以用la先看下

signaltap跑到250M还是挺困难的,可以用100M试试,什么器件,看看timing report有没有timing violation

不知小编signaltap的采样时钟用的是啥?如果跟dina不是一个时钟域,可能会出现问题