数字接收机码元同步探讨,也称位同步

时间:10-02

整理:3721RD

点击:

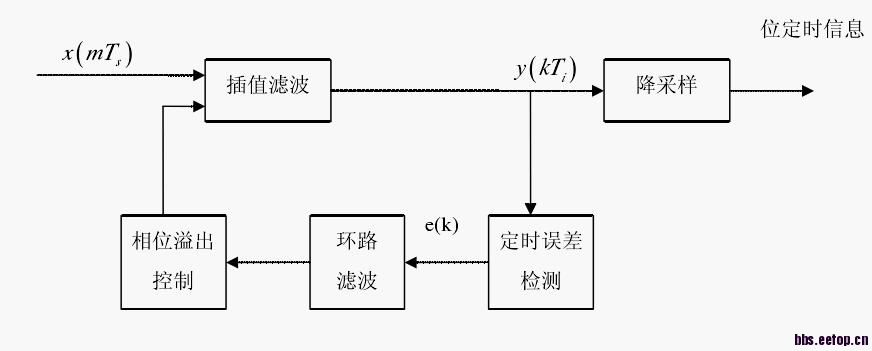

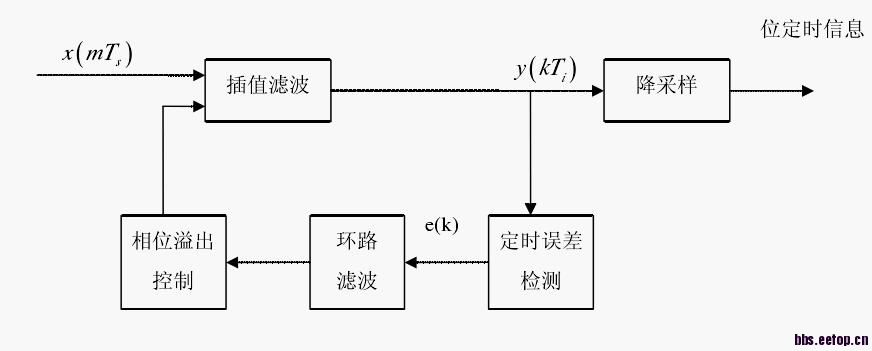

正在设计一个数字接收机如下流程,射频(模拟)-->中频-->基带(4FSK调制)-->码元同步-->帧同步。目前实现到码元同步,采用内插滤波器+gardner误差检错算法。

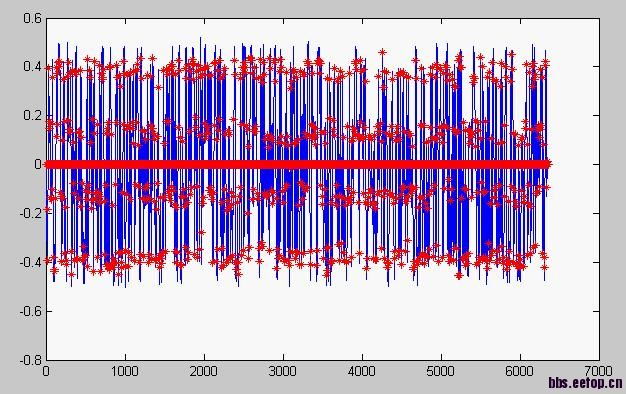

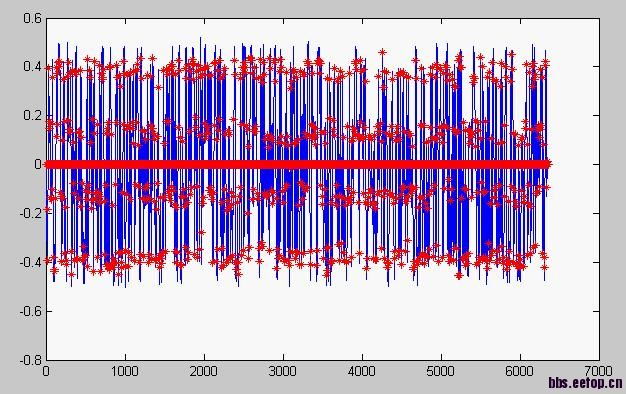

模拟25db AWGN 信道,偏离最佳抽判点+-5%--+-15% 经过插值校正后

抽判结果 4个电平信号抽判很清晰

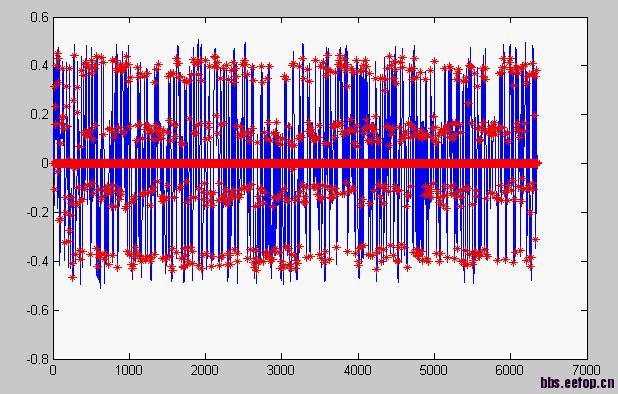

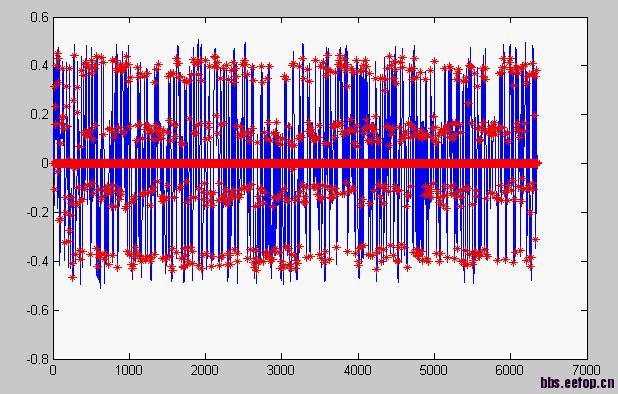

模拟25db AWGN 信道,偏离最佳抽判点+-15%--+-25% 经过插值校正后

抽判结果 4个电平信号抽判经过大概30个符号周期的调整最最终恢复到最佳抽判点

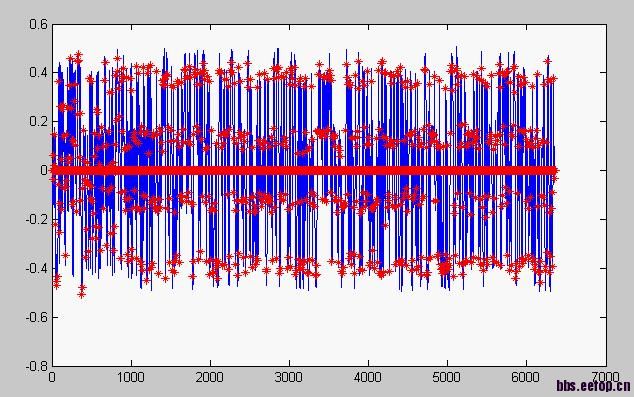

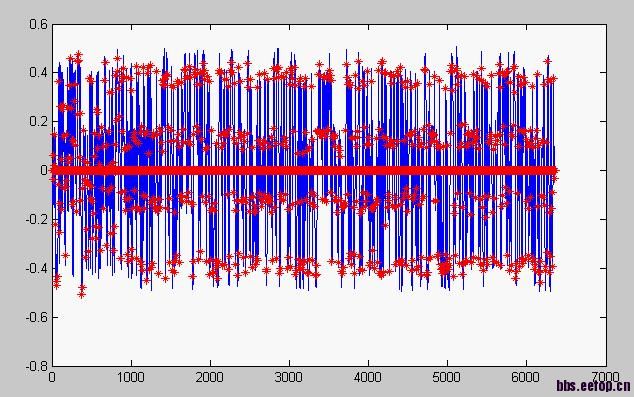

模拟25db AWGN 信道,偏离最佳抽判点+-25%--+-45% 经过插值校正后

抽判结果 4个电平信号抽判经过大概80个符号周期的调整后最终恢复到最佳抽判点。

请问大家根据你们的经验一般从射频到中频再到基带然后抽判,起始的抽判点偏离最佳采样点会在什么范围内呢?+-10% +- 20% +-30% 等等。研究数字接收机的朋友来探讨下。

模拟25db AWGN 信道,偏离最佳抽判点+-5%--+-15% 经过插值校正后

抽判结果 4个电平信号抽判很清晰

模拟25db AWGN 信道,偏离最佳抽判点+-15%--+-25% 经过插值校正后

抽判结果 4个电平信号抽判经过大概30个符号周期的调整最最终恢复到最佳抽判点

模拟25db AWGN 信道,偏离最佳抽判点+-25%--+-45% 经过插值校正后

抽判结果 4个电平信号抽判经过大概80个符号周期的调整后最终恢复到最佳抽判点。

请问大家根据你们的经验一般从射频到中频再到基带然后抽判,起始的抽判点偏离最佳采样点会在什么范围内呢?+-10% +- 20% +-30% 等等。研究数字接收机的朋友来探讨下。

自己顶一个没人研究过同步算法?