自己创建的ROM读不出来数据

时间:10-02

整理:3721RD

点击:

module memory_tb;

// Inputs

reg clk;

reg[6:0] addr;

// Outputs

wire[15:0] dataout;

// Instantiate the Unit Under Test (UUT)

memory uut (

.clk(clk),

.addr(addr),

.dataout(dataout)

);

initial begin

clk = 1'b0;

addr = 16'h0001;

end

always

clk = #(5/2) ~clk;

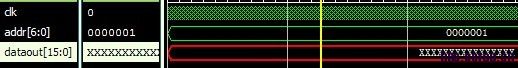

这是自己的testbench,创建的ROM为16bit*100,而且已经读入ceo文件了,但是为什么仿真的时候读不出来数据呢

dataout一直是16‘h0000.

你这个问题不好判断....

你最好给出仿真波形....

initial begin

clk = 1'b0;

addr = 16'h0001;

end

地址线始终在16'h0001,根本没动过,当然一直是1个值。

刚才仿真下,现在是根本没有数据了,一直是XXXX,读取不出来的

把完整的东西发上来再说。

你clk是否满足该mem的时序要求?

CEO文件是什么意思?

对于altera,应该是mif文件。

你把信号截图放完整...你这个图不能确定你的ROM里面真的有数据....