怎样用verilog实现纯数字的倍频电路?

时间:10-02

整理:3721RD

点击:

请教大家,谢谢!

理论上是可以的

但是很难得到占空比是50%的时钟。

同求解答,这个以前只知道是分频,还真没有弄过倍频的

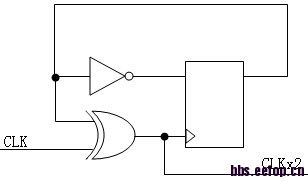

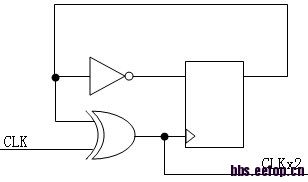

下面这个图可以用来倍频。

利用了寄存器传播延时。

仿真的话,必须给FF加传播延时。

不过占空比很难控制到50%。

用倍频模块不行吗?

倍频一般都是用模拟做吧,数字的优势不在这方面

放着PLL和DCM不用为啥非要用数字实现?

能否先用计数器类似的东西提取原频率,同时生成倍频的。

关键在于如何提取频率,数字提取频率原理要比pll容易?个人觉得是这样

pll能否数字化呢

有全数字的PLL,但是随着对clock频率要求越来越高,还是要依靠模拟电路的PLL来实现。

module beipin(clk,ret,clk1);

input clk,ret;

output clk1;

reg data;

always @(posedge clk1 or negedge ret)

if(!ret)

data<=0;

else

data<=~data;

function clk2;

input clk,data;

begin

clk2=!clk&&data||!data&&clk;

end

endfunction

assign clk1= clk2(clk,data);

endmodule

这是我根据你的电路图写的程序

为什么要把pll数字化,IC内部如果要提高系统频率一般都会用pll,fpga的话更方便,内部自己就有的啊