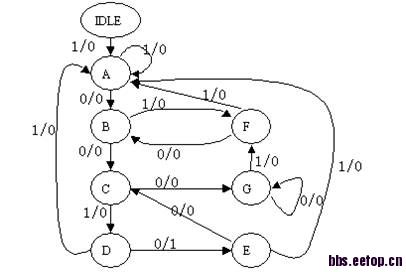

序列检码器 状态机 的一点小疑问

时间:10-02

整理:3721RD

点击:

我有一点不明白, 在状态B的情况下要是输入1的话,直接进入A状态不行么?G状态下如果输入1的话也可以直接进入A状态啊,我就是这样做的一个状态机,也实现了这个序列的功能要求,重叠的码也能检测出来,所以我想问问 这个F 状态到底有什么用啊?如果没有什么实质的作用那多一个状态岂不是多占用了资源?

你这是检测什么码呢 总要说下吧

这个是夏宇闻的那本书上的例题吧我之前学的时候也是同样的疑问那两个多余的状态可以省略还有如果你写状态机的话建议搜索三段式状态机的写法~夏宇闻那本书的状态机写法落后都是一段式的~

这个是夏宇闻的那本书上的例题吧我之前学的时候也是同样的疑问那两个多余的状态可以省略还有如果你写状态机的话建议搜索三段式状态机的写法~夏宇闻那本书的状态机写法落后都是一段式的~

嗯 我也是感觉这状态多余 现在一般 三个always 描述状态机 是吧 一个描述功能 一个描述组合逻辑 一个描述输出 eeworld上有个高手说这个检码器能用一个滑动窗口解决 滑动窗口是个什么东东?

简单状态机一段没问题,复杂点还是三段好,直观、容易分析。

移动窗口大概是这样:

din_tmp(7 downto 0)= din_tmp(7 downto 1) & din;

然后每个clk对din_tmp判断一次等不等于序列值就行了

这样说滑动窗口 还是不懂 我在网上搜过 好像是一种通信协议 您能详细点 具体点给我解释一下么

滑动窗口好像TCP/IP里面有这个概念。