高手看过来:Altera中数据写入RAM时的时钟有效沿

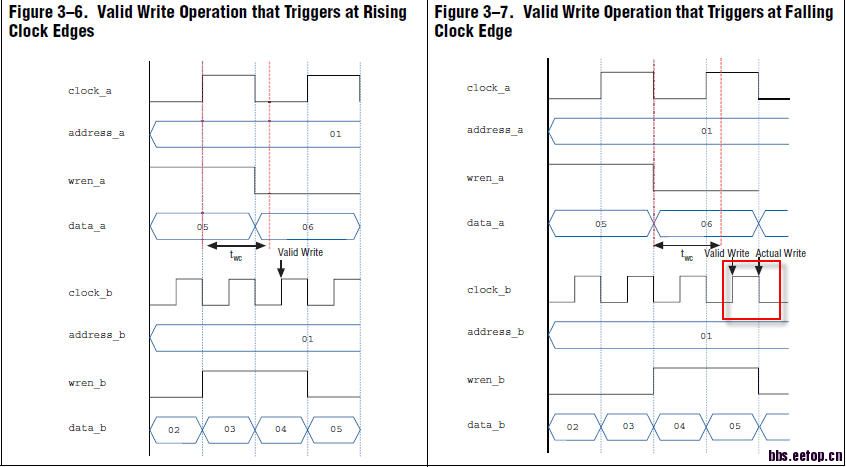

小弟很疑惑,M4K为什么不在锁存数据的上升沿时刻同时将数据保留到RAM中,而是要多等半个时钟才保留数据,也就是所谓的trigger。望高人指教!这样就相当于用倍频时钟采样原始数据,只会让时序更坏呀,真是疑惑啊。

应该是RAM的后端实现的限制,不是设计上的考虑

哥,看你今天上网兴许是心血来潮一口气回了不少帖子,但建议请讲得稍微详细点吧。

“ 应该是RAM的后端实现的限制,不是设计上的考虑”,后端限制了什么,为什么要限制?

你操作ram只需要关心端口时序,至于内部怎么实现的,不需要知道,如果你想知道,你可以找一下ram的实现原理方面的知识

谢谢您的回复。我只是想从宏观角度去尝试了解它的意图,而不是轻易地接受某些事实,限于工作原因也没有精力去涉猎相关书籍(哎,惭愧),所以放在此地,希望集思广益,抛砖引玉,望路过的大牛们不吝赐教!或者请solarwafer兄能推荐下关于这方面的书籍以待闲暇时看看。直觉上,个人认为altera的RAM使用上升沿或者下降沿trigger数据看似为对称的两面,都是可以的。可为什么M4K型偏偏采用下降沿trigger方式,难道M4K型RAM单元与其他单元相比更适合施加约束以用倍频时钟来trigger前个上升沿锁存的数据。

因为寄存器的原因,可能有个概念你不理解,数字电路中的寄存器trigger也叫flipflop也叫register,是由两级锁存latch组成的,前后两级用反向时钟控制,建议你看下大规模集成电路的书。当时钟上升沿过来的数据还只是存在寄存器中,也就是第一级latch,在下降沿来到的时候才通过第二级latch输入到双稳态中,一般我们用的都是下降沿触发的trigger,也就是第一级用正向时钟控制。

谢谢您的回复!参考Altera手册的意思,trigger的含义不一定是指register,而是强调RAM单元保存好了数据这一状态。你后半部分理解的很对,尤其是两级寄存器用反向时钟级联这点是切中要害!其实质就是用下降沿锁存前一个上升沿锁存好的数据,但这更容易导致时序问题。

另外“一般我们用的都是下降沿触发的trigger,也就是第一级用正向时钟控制。”什么意思?要知道,我们通常用的是上升沿触发的寄存器哦。但以上这些还不是我的疑问所在。问题的核心是Altera为什么会对不同类型的内部RAM Block(如M4K,M9K,M512K等等)在写入时采用不同的锁存数据方式?这才是核心疑团!欢迎前辈们积极探讨,踊跃发言。

既然M4K使用了类似两级Latch锁存的原理,那么怎么解释图中只采用上升沿触发register的情形。你不会认为也是两级Latch吧。第一级采用下降沿,第二级采用上升沿?

是的,你在valid和actucl之间的时间数据是在latch的第一级,可能为了采到比较稳定的数据而采用REG,一级latch很可能因为时序问题而锁到一个错误值,还有你说的时序问题,我看了下你的图,如果是reg的话,它很可能用了倍频时钟来读写数据,这样是不会出现时序问题的,而且更加保证了读写数据的正确性。

按照你的意思,上面左图可能是采用了两级Latch的思想;而右图则为了避免第二级Latch锁存时刻数据已经不稳定而可能采用倍频时钟方式。不知这样理解对吗?但为什么会存在这两种差异,也就是为什么会有这两种RAM块写操作方式了?两种实现方式消耗的资源可是差不多啊,并且后者还需要产生一个反向时钟(或者倍频时钟)及相应的约束。换句话说,右图方式更复杂一点。

左图是一级latch,valid写既actual写。右图是两级latch,更正下,两面都没有倍频,只是右图actual写的数据比左图延迟了半个时钟周期,原因我上面说了,为了采到更稳定准确的数据。