初学者问个简单的问题 希望高手不要觉得太简单而不回答

有几个高手进来看过了,怎么就不回复一下呢。大神帮帮忙啊,耽误您几分钟,麻烦您指点迷津。再次表示感谢了

用门级电路描述?与非门?

怎么描述呢?门级电路没法表示触发信号,也许是我不懂。求更多点指导

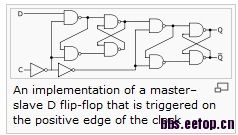

For a positive-edge triggered master–slave D flip-flop, when the clock signal is low (logical 0) the "enable" seen by the first or "master" D latch (the inverted clock signal) is high (logical 1). This allows the "master" latch to store the input value when the clock signal transitions from low to high. As the clock signal goes high (0 to 1) the inverted "enable" of the first latch goes low (1 to 0) and the value seen at the input to the master latch is "locked". Nearly simultaneously, the twice inverted "enable" of the second or "slave" D latch transitions from low to high (0 to 1) with the clock signal. This allows the signal captured at the rising edge of the clock by the now "locked" master latch to pass through the "slave" latch. When the clock signal returns to low (1 to 0), the output of the "slave" latch is "locked", and the value seen at the last rising edge of the clock is held while the "master" latch begins to accept new values in preparation for the next rising clock edge.

dff

thank you!看来是数电的知识不扎实,要去看看触发器的基本结构。在此表示感谢~

时钟沿敏感,把输入赋给输出

module D_FF(

clk,

rst_n,

in,

out);

input clk,rst_n;

input in;

output reg out;

always @(posedge clk,negedge rst_n)

if(!rst_n)

out<=1'b0;

else

out<=in;

endmodule

80年代商用结构不是6个与非门吗,貌似分析一遍可以杀死很多脑细胞的……

打算使用RTL在门级搭一个DFF?目的何在呢?

理论上,你可以找到一个DFF的门级结构图,然后一个门一个门的例化,这就是一个DFF。

但是DFF中有组合逻辑的反馈,也就是组合逻辑环。

因为有组合逻辑环在,应该是不可综合的,仿真可能也会卡住。

没有试过这东西,正常代码中应该避免组合逻辑环。

D触发器啊 直接写程序