xilinx FIFO IP核前仿和后仿读数据少了3个,真奇怪!

independent clk syn standard fifo.120x32bit.

仿真时先写入1,2,3……,然后读出来

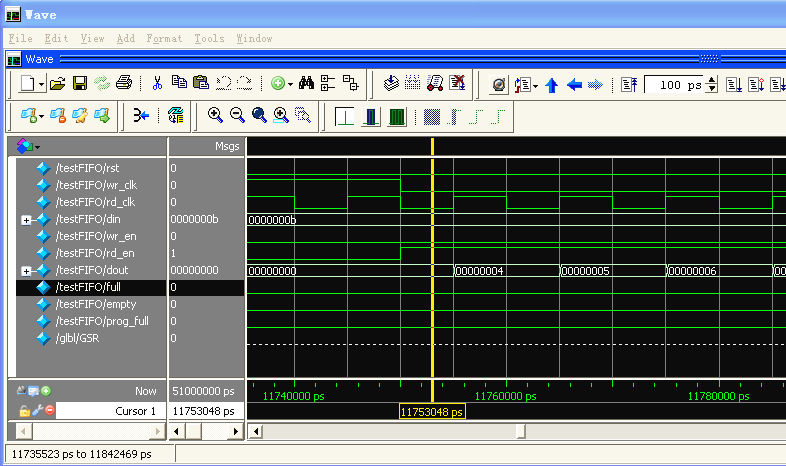

前仿真完全正确,后仿真时读出数据则从4开始。不知为什么?非常奇怪!

有人说xilinx的ip fifo需要free running 时钟,testbech里面使用了啊,问题依旧。

这个我在硬件上实现了,和后仿结果一致。【xc5vsx50t ff665-2】ise10.1。

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer:

//

// Create Date: 21:14:31 12/31/2010

// Design Name:

// Module Name: FIFOwei

// Project Name:

// Target Devices:

// Tool versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//////////////////////////////////////////////////////////////////////////////////

module FIFOwei(

input rst,

input wr_clk,

input rd_clk,

input [31 : 0] din,

input wr_en,

input rd_en,

output [31 : 0] dout,

output full,

output empty,

output prog_full

);

FIFO_120x32 YourInstanceName (

.rst(rst),

.wr_clk(wr_clk),

.rd_clk(rd_clk),

.din(din), // Bus [31 : 0]

.wr_en(wr_en),

.rd_en(rd_en),

.dout(dout), // Bus [31 : 0]

.full(full),

.empty(empty),

.prog_full(prog_full));

endmodule

、、-----------------------------------------------

test bench

`timescale 1ns / 1ps

////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer:

//

// Create Date: 20:22:07 12/31/2010

// Design Name: FIFO_120x32

// Module Name: D:/08MyFpga/Virtex5FIFO/testFIFO.v

// Project Name: Virtex5FIFO

// Target Device:

// Tool versions:

// Description:

//

// Verilog Test Fixture created by ISE for module: FIFO_120x32

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

////////////////////////////////////////////////////////////////////////////////

module testFIFO;

// Inputs

reg rst;

reg wr_clk;

reg rd_clk;

reg [31:0] din;

reg wr_en;

reg rd_en;

// Outputs

wire [31:0] dout;

wire full;

wire empty;

wire prog_full;

// Instantiate the Unit Under Test (UUT)

FIFOwei uut (

.rst(rst),

.wr_clk(wr_clk),

.rd_clk(rd_clk),

.din(din),

.wr_en(wr_en),

.rd_en(rd_en),

.dout(dout),

.full(full),

.empty(empty),

.prog_full(prog_full)

);

initial

forever

begin

rd_clk = 0;

#5;rd_clk=1;

#5;

end

/*

initial begin

forever

wr_clk = 0;

#20;wr_clk=1;

#20;

end

*/

initial begin

// Initialize Inputs

rst = 0;

wr_clk = 0;

din = 0;

wr_en = 0;

rd_en = 0;

// Wait 100 ns for global reset to finish

#500;

wr_en=1;

#50;din=1;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=2;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=3;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=4;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=5;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=6;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=7;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=8;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=9;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=10;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=11;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=12;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=13;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=14;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=15;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=16;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=1;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=2;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=3;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=4;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=5;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=6;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=7;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=8;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=9;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=10;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=11;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=12;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=13;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=14;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=15;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=16;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=1;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=2;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=3;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=4;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=5;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=6;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=7;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=8;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=9;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=10;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=11;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=12;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=13;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=14;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=15;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=16;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=1;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=2;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=3;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=4;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=5;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=6;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=7;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=8;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=9;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=10;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=11;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=12;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=13;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=14;

wr_en=0;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=15;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=16;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=1;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=2;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=3;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=4;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=5;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=6;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=7;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=8;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=9;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=10;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=11;

#50;wr_clk=1;

#50;wr_clk=0;rd_en=1;

#50;din=12;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=13;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=14;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=15;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=16;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=1;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=2;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=3;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=4;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=5;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=6;rd_en=0;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=7;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=8;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=9;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=10;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=11;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=12;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=13;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=14;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=15;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=16;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=1;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=2;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=3;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=4;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=5;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=6;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=7;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=8;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=9;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=10;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=11;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=12;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=13;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=14;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=15;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=16;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=1;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=2;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=3;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=4;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=5;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=6;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=7;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=8;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=9;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=10;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=11;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=12;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=13;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=14;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=15;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=16;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=1;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=2;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=3;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=4;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=5;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=6;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=7;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=8;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=9;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=10;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=11;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=12;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=13;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=14;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=15;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=16;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=1;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=2;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=3;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=4;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=5;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=6;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=7;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=8;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=9;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=10;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=11;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=12;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=13;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=14;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=15;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=16;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=1;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=2;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=3;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=4;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=5;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=6;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=7;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=8;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=9;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=10;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=11;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=12;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=13;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=14;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=15;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=16;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=1;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=2;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=3;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=4;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=5;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=6;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=7;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=8;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=9;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=10;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=11;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=12;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=13;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=14;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=15;

#50;wr_clk=1;

#50;wr_clk=0;

#50;din=16;

#50;wr_clk=1;

#50;wr_clk=0;

/*

#50;wr_en=0;

#500;

#52;rd_en=1;

#1500;rd_en=0;

*/

#1000;

// Add stimulus here

end

endmodule

modelsim使用6.5

硬件实现的时候约束仅仅对管脚进行了位置约束,其余没有。

上面的仿真后仿时管脚使用软件的自动配置,即本人未使用ucf文件。

谢谢大侠相助!

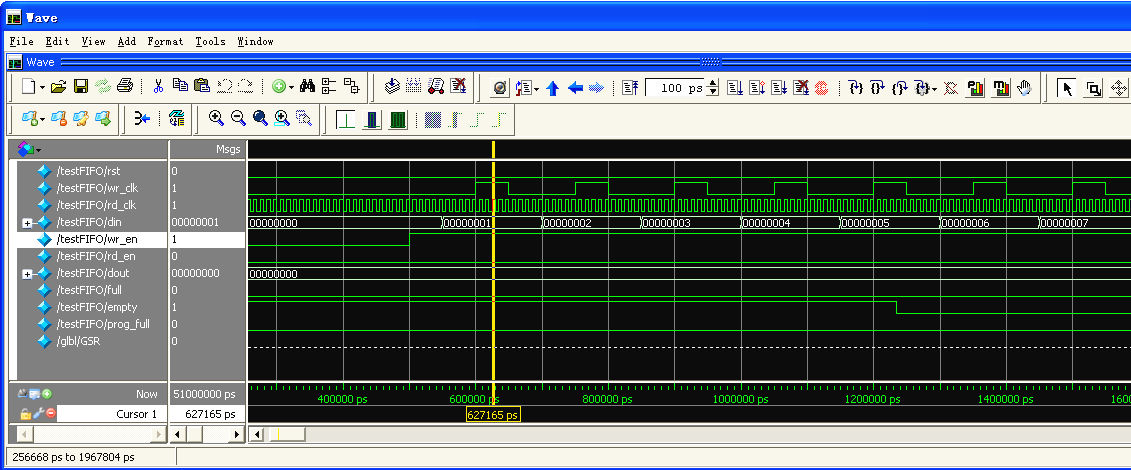

看你的写时钟和数据就对不上啊。写时钟不是周期?异步的话出问题也正常啊,testbench写的也太诡异了吧。为什么不产生一个时钟,就写always产生din呢?testbench中时钟也不像你那样产生吧。

ug175里有写复位是有3个周期左右的延迟

关键是你这个在写之前都没有时钟,因为到内部逻辑的复位信号都是同步到读写时钟的,而你在复位时却没有时钟,很难保证仿真模型的行为描述是否会产生异常。

谢谢gg9132qq

谢谢小编:)

“关键是你这个在写之前都没有时钟”

我在wr_en前又加了若干个wr_clk

后仿真正常了,谢谢了:)

=======================

gg9132qq

说的问题,其实写时钟为了正好处于数据有效的中间,如下图

_____________________________________

----------<==========><==============>---------

学习了,谢谢~

看波形是没写进去,不过你后边自已解决了.呵呵,我也学习了.谢谢.

非常感谢诸位的帮助!

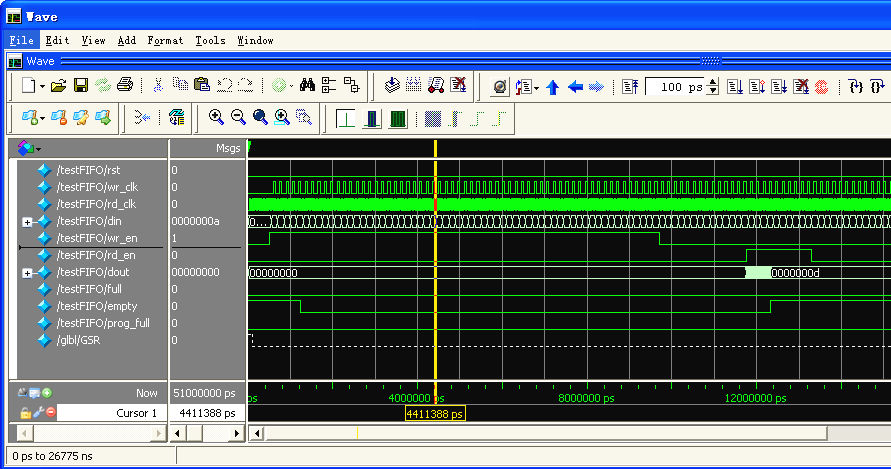

这个问题的原因确实就是wr_en之前没有wr_clk的原因造成的。

本人编制的程序对写fifo不期望使用free running clk。因为数据采集是一批一批的,来一批写一次fifo。

最终处理的时序略图如下:

信号名称从上到下依次为:wr_en,wr_clk,wr_data.wr_clk在wr_en有效值1前后各加了6各clk。

使用一切正常,已经下载到fpga验证正确。

___________________________

_~_~_~_~_~_______________________________________~_~_~_

-----------------------<=======><=======><========><=======><=======>-------------

再次对小编和各位热心的仁兄表示感谢!

本人的电路板基于tms320c6455+Virtex5sx50T+1Gnet+24ADC+2HiDAC+4LoDAC+2RS232+2RS422+SRIO.

欢迎大家交流:)

为啥不用free running clk?对功耗要求很严格?

也在学习,希望有用

请教:为什么我的fifo在复位后(rest_fifo)后,empty和full都为1,并且wr_ack一直为0?谢谢

自己解决了,原来在生成fifo时,有个reset后full flag的值是1还是0的选项,改成0就可以了