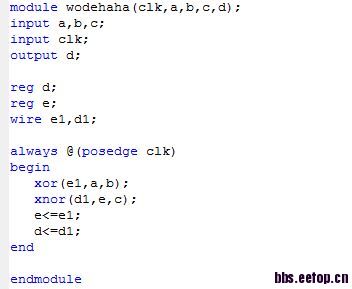

用门级的verilog来写时序电路就搞不定了,请帮帮忙

你就没写对!既然你想用门来搭电路,就不例化单元?都是门级了还用always模块?

用门级我写不出来,只能用单元来实现

xor2x1 u1 (.y(e1),

.a(a),

.b(b));

xnor2x1 u2 (.y(d1),

.a(e),

.c(c)

);

DFFX1 u3(.q(e),

.d(e1),

.ck(clk));

DFFX1 u4 (.q(d),

.d(d1),

.ck(clk));

完了!

我真是蛋疼

);

always块里只有过程块语句,没有模块调用!

你要是非得这么写,也得把xor之类的东西放到always外面

谢谢你,我好好看看,基础还是不扎实

谢谢,我再看看always的语法

我之前移到过外面,可是提示还是不对,谢谢大家给我的帮助

语法问题

改为

xor xor1(e1,a,b);

还有你的a,b总该也声明一下wire啊

2楼说的对,ALWAYS只能用在逻辑功能描述。门级不能用always

直接我上面的那段描述就行了

本人是在ISE里面做的,之前一直想在verilog中找flipflop,可是verilog没有这个原语,然后ise里面可以用FD作为D触发器用,所以现在能自己搭电路了,我还总结了几页纸,大家如果感兴趣我可以发给大家,谢谢大家的关照

本人是在ISE里面做的,之前一直想在verilog中找flipflop,可是verilog没有这个原语,然后ise里面可以用FD作为D触发器用,所以现在能自己搭电路了,我还总结了几页纸,大家如果感兴趣我可以发给大家,谢谢大家的关照

可以写个always嘛

wonderful~