三分频电路跑不到100MHz? 求高人解答

/////////////////////////////////////////////////

module div3(clk,rst,div_clk);

input clk;

input rst;

output div_clk;

wire div_clk;

reg [1:0] count_a;

reg [1:0] count_b;

always@(posedge clk)

if (!rst)

count_a <= 0;

else

begin

count_a <= (count_a == 2)? 0 :count_a+1;

end

always@(negedge clk)

if (!rst)

count_b <= 0;

else

begin

count_b <= (count_b == 2)? 0 :count_b+1;

end

assign div_clk = ((count_a!=2)&&(count_b!=2));

endmodule

/////////////////////////////////////////////////

Quartus10.1的版本综合,综合没改其他约束,器件选的是stratixii

用TimeQuest分析,约束文件如下

create_clock -name clk -period 10.000 -waveform {0 5} [get_ports clk]

set_input_delay -clock { clk } -max 2 -add_delay [get_ports rst]

set_output_delay -clock { clk } -max 2 -add_delay [get_ports div_clk]

create_generated_clock -name clkb0 -source [get_ports {clk}] -invert [get_pins {count_b[0]|clk}]

create_generated_clock -name clkb1 -source [get_ports {clk}] -invert [get_pins {count_b[1]|clk}]

/////////////////////////////////////////////////

时序分析结果,直接上图

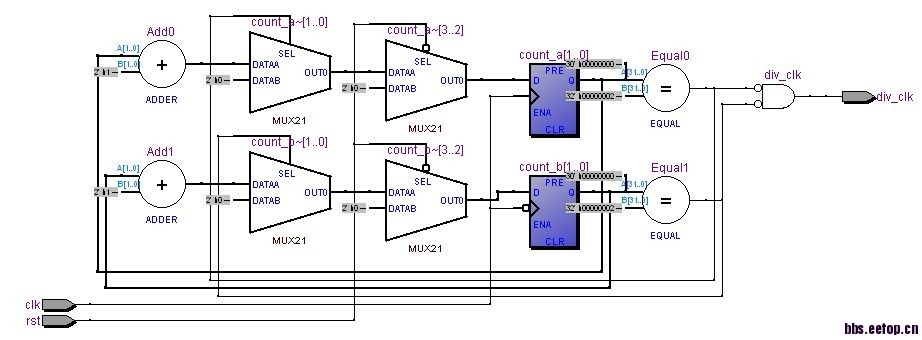

先给个综合的RTL图

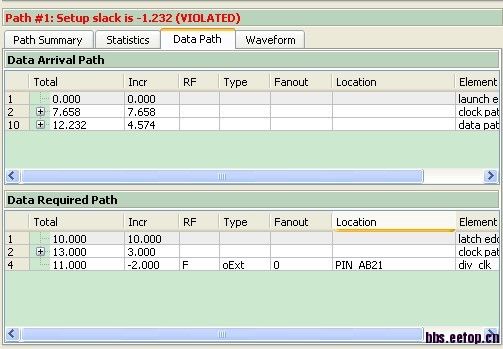

然后是时序分析报告:

可以看到时序违例都是inter to output的

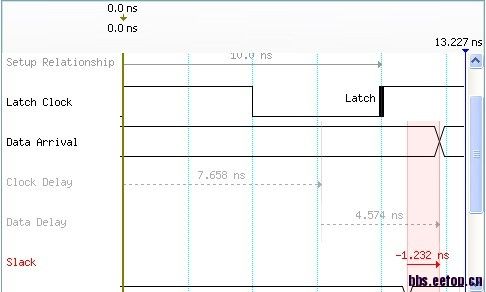

波形如下,最下面的是Data Required Time

我不明白的是clock delay怎么会那么大,一个简单的三分频电路跑不到100MHz

求高手解答

组合逻辑较多,可加下pipeline

或考虑将div_clk加约束用上全局时钟网络,

或者用原时钟,把分频时钟当使能信号来用,或者用PLL等分来的时钟,一般不建议使用寄存器分频,尤其在高速时。

这个组合逻辑也算多么? 应该不至于啊,寄存器前一级一个加法器两个Mux,后一级一个比较器,一个非门,一个与门

感觉这是一个比较简单的电路了,这样的组合逻辑300M跑不到就算了,100M都跑不到

是不是要从器件映射底层去看组合逻辑?

当然,我做工程的时候也是用PLL来分、倍频,只是刚好综合了一个寄存器分频电路,又时序分析了下,发现100M都跑不到,就上来问问啦

100M对于FPGA来说算中等,不算太高频吧。

不考虑在系统电路中用div_clk,只是看分频电路,div_clk时序违例,难道真是那几个组合逻辑的问题?

当然,我做工程的时候也是用PLL来分、倍频,只是刚好综合了一个寄存器分频电路,又时序分析了下,发现100M都跑不到,就上来问问啦

100M对于FPGA来说算中等,不算太高频吧。

不考虑在系统电路中用div_clk,只是看分频电路,div_clk时序违例,难道真是那几个组合逻辑的问题?

写的这种三分频没什么实际用处,不建议那样用。

001 010 100 三状态

你的意思是写状态机,那不就把简单的问题复杂了么,状态机时序上或许会好些

如果在FPGA中,你要用到时钟negative沿触发,最好先做一个clkb = ~clka,然后将clkb从bufg中走一下,这样你的clkb的延时就会小很多。

因为在综合的时候,你分频的这个时钟若用作其他器件的时钟来使用时,会自动加上全局时钟buffer,时钟信号进全局时钟buffer时,是会有很大的延时的。

clkb = ~clka,这就等于在时钟上加逻辑,这样会不会使clock_uncertain变的更不稳定?

另外,弱弱的问一句,一般在FPGA中,negedge是怎么实现的?

“

然后将clkb从bufg中走一下” 我想问下bufg在Altera里有没有,应该怎么设置?

目前这个电路还没把分频的时钟当成其他电路的时钟来用

现在这个时钟理解成只是一个output,也会加全局buffer么?