IDDR原语问题求教

时间:10-02

整理:3721RD

点击:

小弟初用IDDR原语想实现数据降频,verilog语句如下:

module IDDR_primitive(

input C,

input CE,

input R,

input S,

input [7:0] D,

output [7:0] Q1,

output [7:0] Q2

);

IDDR #(

.DDR_CLK_EDGE("SAME_EDGE"), //

.INIT_Q1(1'b0),

.INIT_Q2(1'b0),

.SRTYPE("SYNC")

) IDDR_inst (

.Q1(Q1), // 1-bit output for positive edge of clock

.Q2(Q2), // 1-bit output for negative edge of clock

.C(C), // 1-bit clock input

.CE(CE), // 1-bit clock enable input

.D(D), // 1-bit DDR data input

.R(R), // 1-bit reset

.S(S) // 1-bit set

);

endmodule

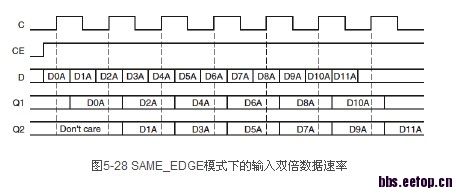

资料上的时序图如下:输入是双数率,上升沿和下降沿,输出双通道都是上升沿输出

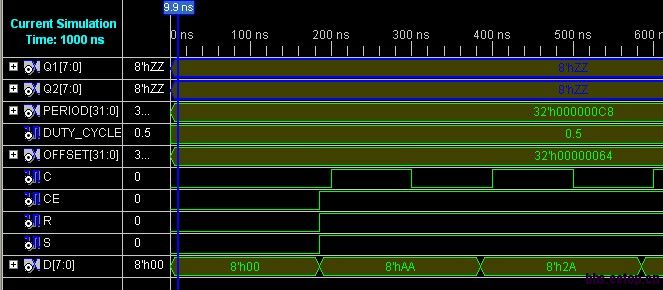

可是小弟仿真的时候

却不是这样的

D为输入端,输入端的数据在一个时钟周期内都是单数率

而且输出数据Q1和Q2两路都是高阻态

小弟新手

求师兄师姐指点

小弟今天又弄了下 确实由于自己没接触过 所以弄错了

1:IDDR处理的数据位数是1位,我弄成了8位

2:在testbench里有个选项是双边缘的,我也没看清楚

自己给自己解答 虽然是小问题 希望以后有像我这样才入门的同学看见 有些帮助